Motorola DSP96002 User Manual

Page 804

22

MOTOROLA

5.3

Obtaining Cache Information Through the OnCE

The OnCE allows the user to keep track of the eight tag values, tags lock/unlock status,

and LRU status. In the OnCE, nine 32-bit registers are implemented as a circular buffer

with a 4-bit counter. All these registers have the same address but any access to the tags

buffer in the cache controller will cause the counter to increment, and thus point to the next

register in the circular buffer. When the processor leaves the debug mode, the counter is

cleared. When the processor enters debug mode again, the first read from the tags buffer

address will always start from the first of the nine registers (tag number 0) and will contin-

ue circularly among them.

The registers mapped in the circular tags buffer are shown in Figure 4.

At any point in time at least one lru bit in the “LRU/LOCK status” register will be set. But it

is possible for more than one of the lru bits to be set simultaneously because locked sec-

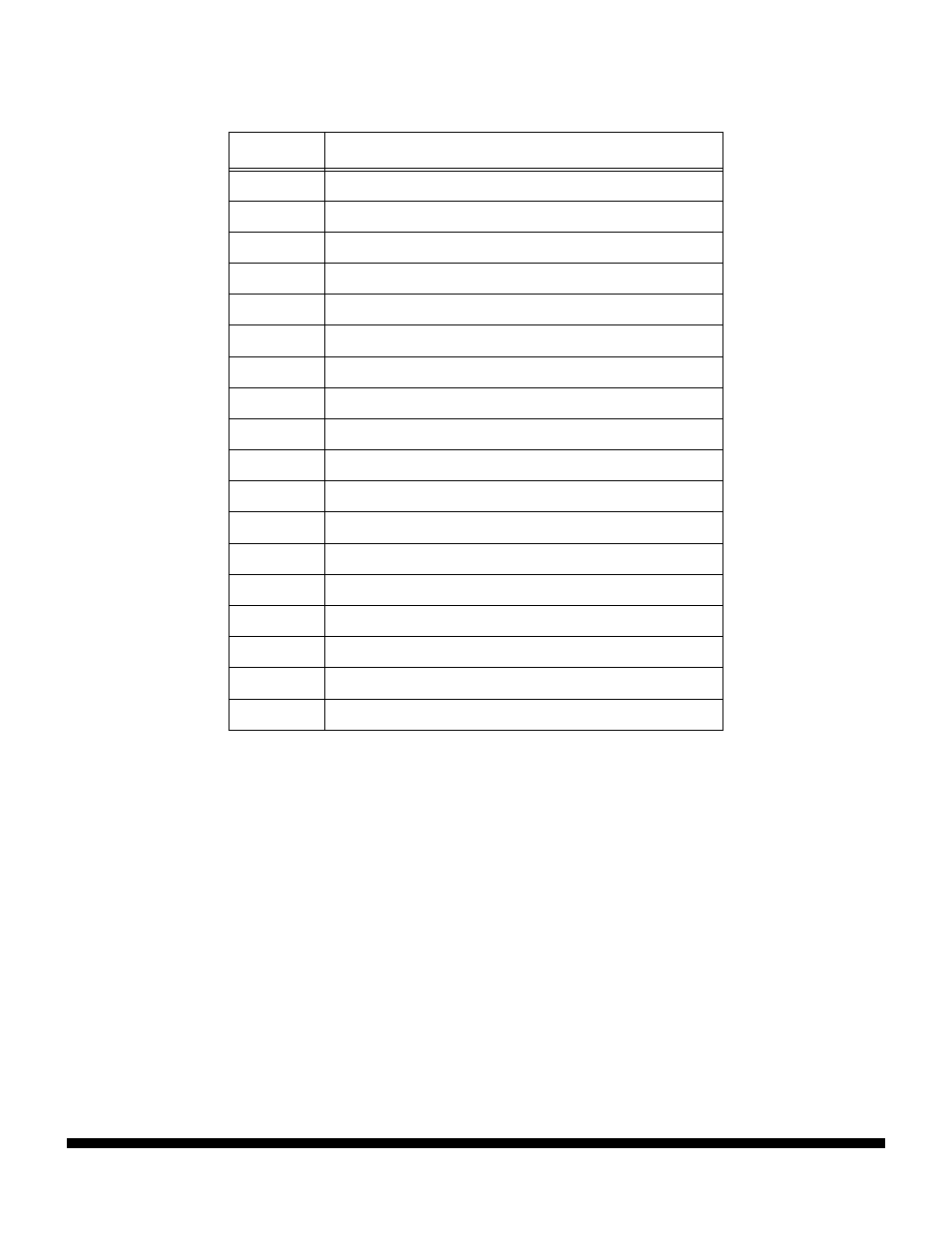

00111

Breakpoint Program Memory Lower-Equal (OPLLR)

01000

Transfer Register (OGDBR)

01001

Program Data Bus Latch (OPDBR)

01010

Program Address Bus Latch for Fetch (OPABF)

01011

Program Instruction Latch (OPILR)

01100

Clear Program Breakpoint Counter

01101

Clear Data Breakpoint Counter

01110

Clear Trace Counter

01111

Reserved

10000

Reserved

10001

Program Address Bus FIFO and Increment Counter

10010

Tags Buffer

10011

Program Address Bus Latch for Decode (OPABD)

101xx

Reserved

11xx0

Reserved

11x0x

Reserved

110xx

Reserved

11111

No Register Selected

Table 1 Register Select Bits 4-0 (RS4-RS0)

RS4-RS0

Register Selected