Loop timing mode, Hdlc overhead controller, Trail trace – Rainbow Electronics DS3170 User Manual

Page 75: Bert, Table 9-18. line ais enable modes, Table 9-19. payload (downstream) ais enable modes, Table 9-18

DS3170 DS3/E3 Single-Chip Transceiver

75 of 233

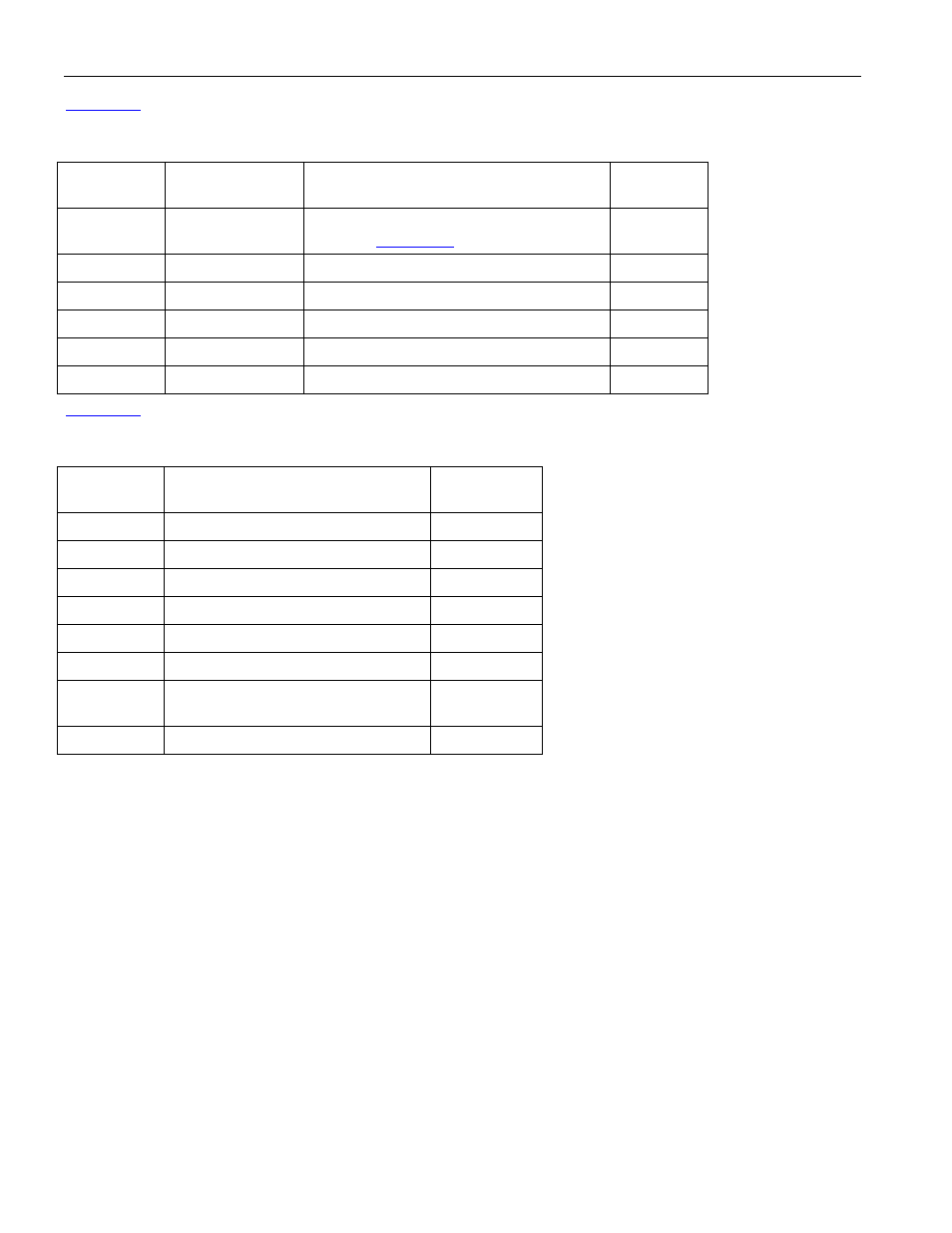

lists the LAIS decodes for various line AIS enable modes.

Table 9-18. Line AIS Enable Modes

LAIS[1:0]

FRAME MODE

DESCRIPTION

AIS CODE

00

DS3

Automatic AIS when DLB is enabled

(

.LBM = 1XX)

DS3AIS

00

E3

Automatic AIS when DLB is enabled

UA1

01 Any

Send

UA1

UA1

10 DS3

Send

AIS

DS3AIS

10 E3

Send

AIS

UA1

11 Any

Disable

none

lists the PAIS decodes for various payload AIS enable modes.

Table 9-19. Payload (Downstream) AIS Enable Modes

PAIS[2:0]

WHEN AIS IS SENT

AIS CODE

000 Always

UA1

001

When LLB (no DLB) active

UA1

010

When PLB active

UA1

011

When LLB(no DLB) or PLB active

UA1

100

When LOS (no DLB) active

UA1

101

When OOF active

UA1

110

When OOF, LOS. LLB (no DLB), or

PLB active

UA1

111 Never

none

9.5.4 Loop Timing Mode

Loop timing mode is enabled by setting the PORT.CR3.LOOPT bit. This mode replaces the clock from the TCLKI

pin with the internal receive clock from either the RLCLK pin if the RX LIU is disabled, or the recovered clock from

the RX LIU if it is enabled. The loop timing mode can be activated in any framing or line interface mode.

9.5.5 HDLC Overhead Controller

The data signal to the receive HDLC controller will be forced to a one while still being clocked when the framer

(DS3, E3), to which the HDLC is connected, detects LOF or AIS. Forcing the data signal to all ones will cause an

HDLC packet abort if the data started to look like a packet instead of allowing a bad, and possibly very long, HDLC

packet.

9.5.6 Trail

Trace

There is a single Trail Trace controller for use in line maintenance protocols. The E3-G.832 framer has access to

the trail trace controller.

9.5.7 BERT

There is a Bit Error Rate Test (BERT) circuit for use in generating and detecting test signals in the payload bits.

The BERT can generate and detect PRBS patterns up to 2^32-1 bits as well as repeating patterns up to 32 bits