Receive pattern detection, Receive prbs synchronization, Table 9-31. pseudo-random pattern generation – Rainbow Electronics DS3170 User Manual

Page 109: Table 9-32. repetitive pattern generation

DS3170 DS3/E3 Single-Chip Transceiver

109 of 233

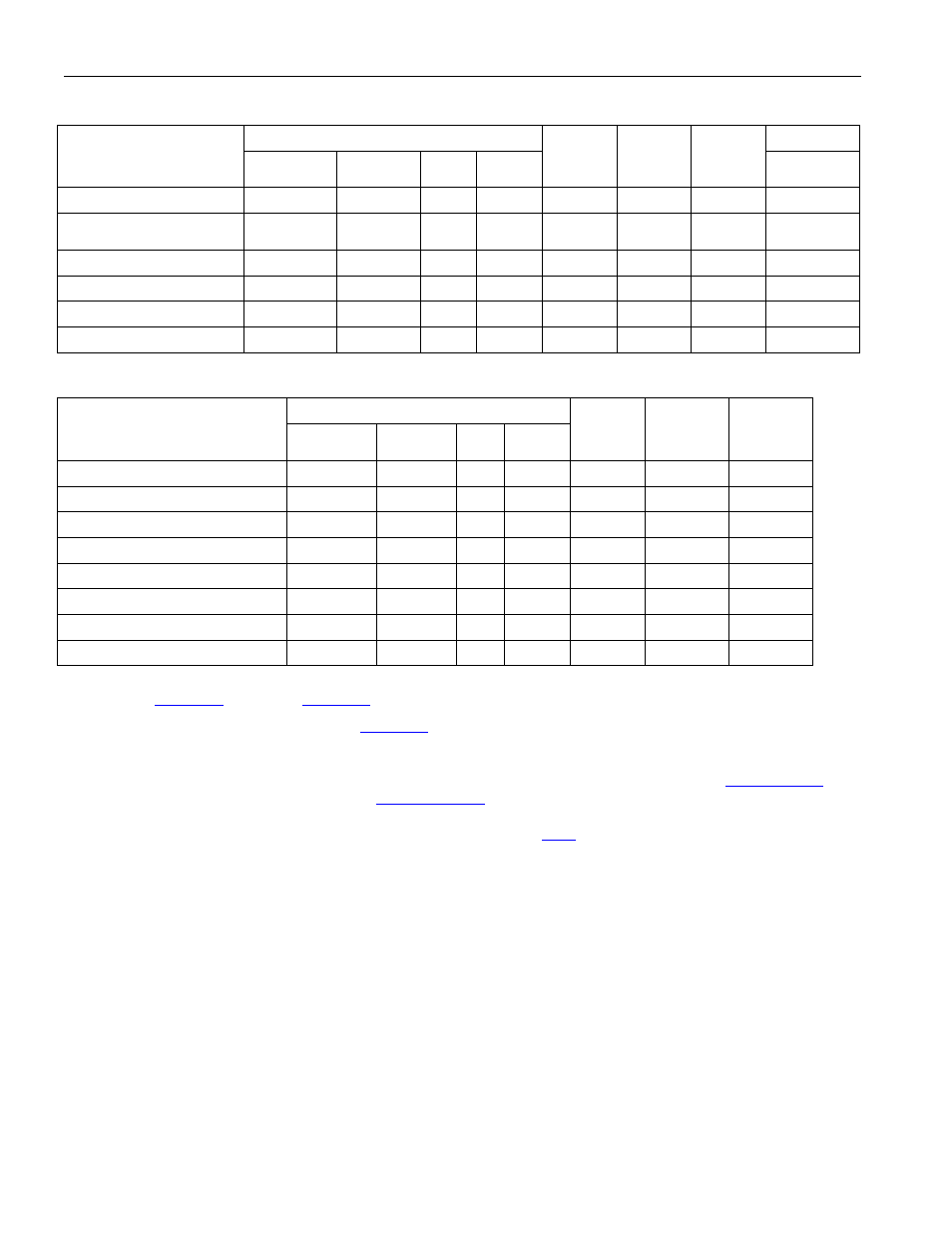

Table 9-31. Pseudo-Random Pattern Generation

BERT.PCR Register

BERT.CR

PATTERN TYPE

PTF[4:0]

(hex)

PLF[4:0]

(hex)

PTS

QRSS

BERT.

PCR

BERT.

SPR2

BERT.

SPR1

TPIC,

RPIC

2

9

-1 O.153 (511 type)

04

08

0

0

0x0408

0xFFFF 0xFFFF 0

2

11

-1 O.152 and O.153

(2047 type)

08 0A

0

0

0x080A

0xFFFF 0xFFFF

0

2

15

-1 O.151

0D

0E

0

0

0x0D0E 0xFFFF 0xFFFF 1

2

20

-1 O.153

10

13

0

0

0x1013

0xFFFF 0xFFFF 0

2

20

-1 O.151 QRSS

02

13

0

1

0x0253

0xFFFF 0xFFFF 0

2

23

-1 O.151

11

16

0

0

0x1116

0xFFFF 0xFFFF 1

Table 9-32. Repetitive Pattern Generation

BERT.PCR Register

PATTERN TYPE

PTF[4:0]

(hex)

PLF[4:0]

(hex)

PTS

QRSS

BERT.

PCR

BERT.

SPR2

BERT.

SPR1

all 1s

NA

00

1 0 0x0020

0xFFFF

0xFFFF

all 0s

NA

00

1 0 0x0020

0xFFFF

0xFFFE

alternating 1s and 0s

NA

01

1 0 0x0021

0xFFFF

0xFFFE

double alternating and 0s

NA

03

1 0 0x0023

0xFFFF

0xFFFC

3 in 24

NA

17

1 0 0x0037

0xFF20

0x0022

1 in 16

NA

0F

1 0 0x002F

0xFFFF

0x0001

1 in 8

NA

07

1 0 0x0027

0xFFFF

0xFF01

1 in 4

NA

03

1 0 0x0023

0xFFFF

0xFFF1

After configuring these bits, the pattern must be loaded into the BERT. This is accomplished via a zero-to-one

transition on

.RNPL

Monitoring the BERT requires reading the

Register which contains the Bit Error Count (BEC) bit and the

Out of Synchronization (OOS) bit. The BEC bit will be one when the bit error counter is one or more. The OOS will

be one when the receive pattern generator is not synchronized to the incoming pattern, which will occur when it

receives a minimum 6 bit errors within a 64 bit window. The Receive BERT Bit Count Register (

) and

the Receive BERT Bit Error Count Register (

) will be updated upon the reception of a Performance

Monitor Update signal (e.g. BERT.CR.LPMU). This signal will update the registers with the values of the counter

since the last update and will reset the counters. Please see section

for more details of the PMU.

9.11.4 Receive Pattern Detection

Since the Receive BERT is always enabled, it can be used as an off-line monitor. The Receive BERT receives

only the payload data and synchronizes the receive pattern generator to the incoming pattern. The receive pattern

generator is a 32-bit shift register that shifts data from the least significant bit (LSB) or bit 1 to the most significant

bit (MSB) or bit 32. The input to bit 1 is the feedback. For a PRBS pattern (generating polynomial x

n

+ x

y

+ 1), the

feedback is an XOR of bit n and bit y. For a repetitive pattern (length n), the feedback is bit n. The values for n and

y are individually programmable (1 to 32). The output of the receive pattern generator is the feedback. If QRSS is

enabled, the feedback is an XOR of bits 17 and 20, and the output will be forced to one if the next 14 bits are all

zeros. QRSS is programmable (on or off). For PRBS and QRSS patterns, the feedback will be forced to one if bits

1 through 31 are all zeros. Depending on the type of pattern programmed, pattern detection performs either PRBS

synchronization or repetitive pattern synchronization.

9.11.4.1 Receive PRBS Synchronization

PRBS synchronization synchronizes the receive pattern generator to the incoming PRBS or QRSS pattern. The

receive pattern generator is synchronized by loading 32 data stream bits into the receive pattern generator, and