Parallel bus mode, Table 17-6. micro interface timing – Rainbow Electronics DS3170 User Manual

Page 224

DS3170 DS3/E3 Single-Chip Transceiver

224 of 233

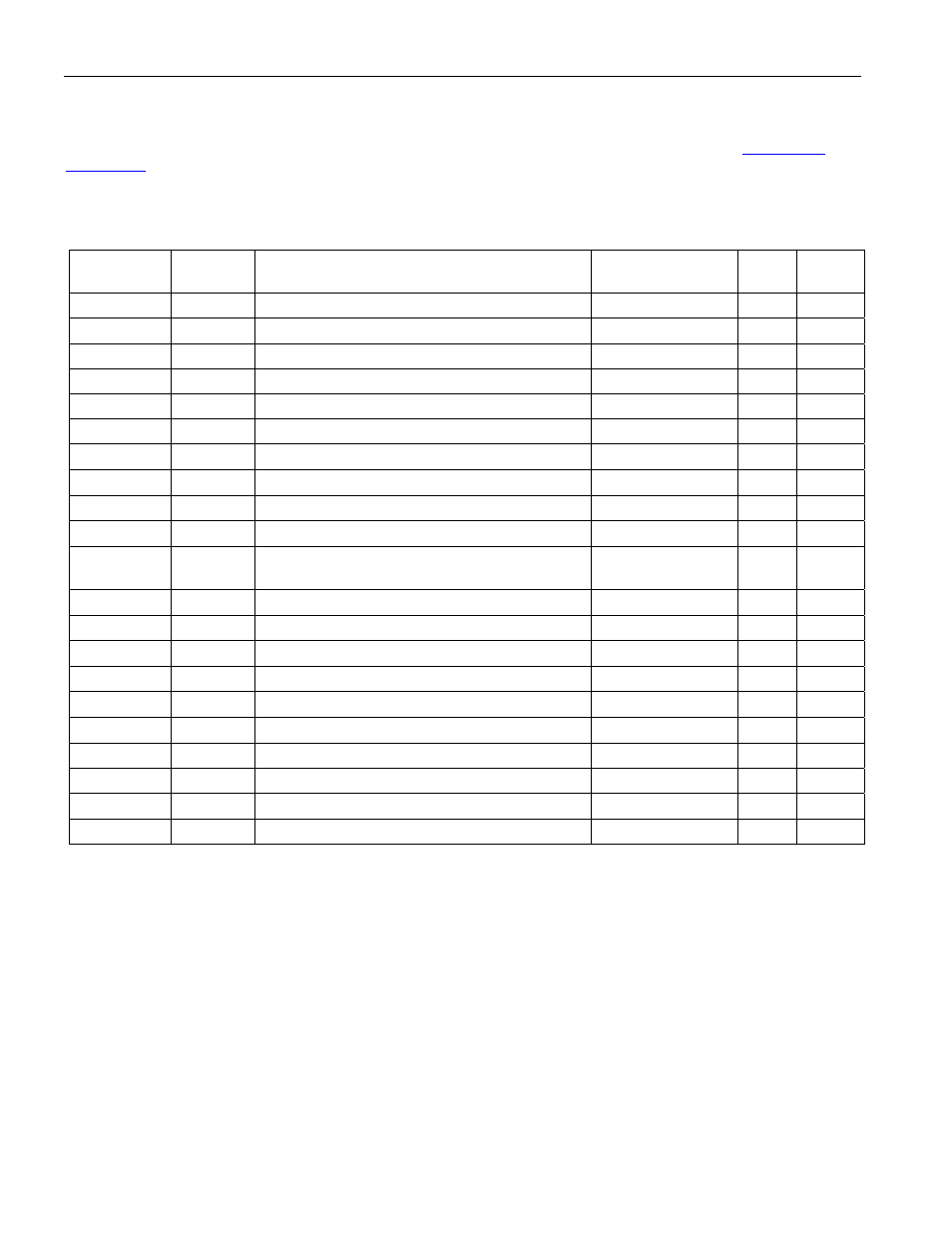

17.3.2 Parallel Bus Mode

The AC characteristics for the external bus interface in parallel mode. This table references

Table 17-6. Micro Interface Timing

(V

DD

= 3.3V ±5%, Tj = -40°C to 125°C.)

SIGNAL

NAME(S)

SYMBOL DESCRIPTION MIN

TYP

MAX

UNITS NOTES

A[N:0]

t1a

Setup Time to

RD, WR, DS Active

10 ns 1

ALE t1b

Setup Time to

RD, WR, DS Active

10 ns 1,

2

A[N:0]

t2

Setup Time to ALE Inactive

2

ns

1, 2

A[N:0]

t3

Hold Time from ALE Inactive

2

ns

1, 2

ALE t4

Pulse

Width

5

ns

1,

2

A[N:0], ALE

t5

Hold Time from

RD, WR, DS Inactive

0 ns 1

CS, R/W

t6

Setup Time to

RD, WR Active

0 ns 1

D[15:0] t8

Output Delay Time from

RD, DS Active

30

ns 1

RD, WR, DS

t9a

Pulse Width if Not Using RDY Handshake

35

ns

1, 4

RD, WR, DS

t9b

Delay from RDY

15

ns

1

D[15:0] t10

Output Deassert Delay Time from

RD, DS

Inactive

2 10 ns 1,

3

CS, R/W

t12

Hold Time from

RD, WR, DS Inactive

0 ns 1

D[15:0] t13

Input Setup Time to

WR, DS Inactive

10 ns 1

D[15:0] t14

Input Hold Time from

WR, DS Inactive

5 ns 1

RDY t15

Delay Time from

RD, WR, DS Active

5 ns 1

RDY t16

Delay Time from

RD, WR, DS Inactive

0 ns 1

RDY t17

Enable Delay Time from

CS Active

18

ns 1

RDY t18

Disable Delay Time from

CS Inactive

12

ns 1

RDY t19

Ending

High

Pulse

Width

1

ns

1

R/

W

t20

Setup Time to

DS Active

2 ns 1

R/

W

t21

Hold Time to

DS Inactive

2 ns 1

Note 1:

The input/output timing reference level for all signals is VDD/2. Transition time (80%/20%) on

RD, WR, and CS inputs is 5ns (max).

Note 2:

Multiplexed mode timing only.

Note 3:

D[15:0] output valid until not driven.

Note 4:

Timing required if not using RDY handshake.