Feac receive side register map, Register bit descriptions, Table 11-19. feac receive side register map – Rainbow Electronics DS3170 User Manual

Page 165: Feac.tsrie, Feac.rcr

DS3170 DS3/E3 Single-Chip Transceiver

165 of 233

Register Name:

FEAC.TSRIE

Register Description:

FEAC Transmit Status Register Interrupt Enable

Register Address:

0C8h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- -- -- -- --

TFIIE

Default

0 0 0 0 0 0 0 0

Bit 0: Transmit FEAC Idle Interrupt Enable (TFIIE) – This bit enables an interrupt if the TFIL bit is set and the bit

in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

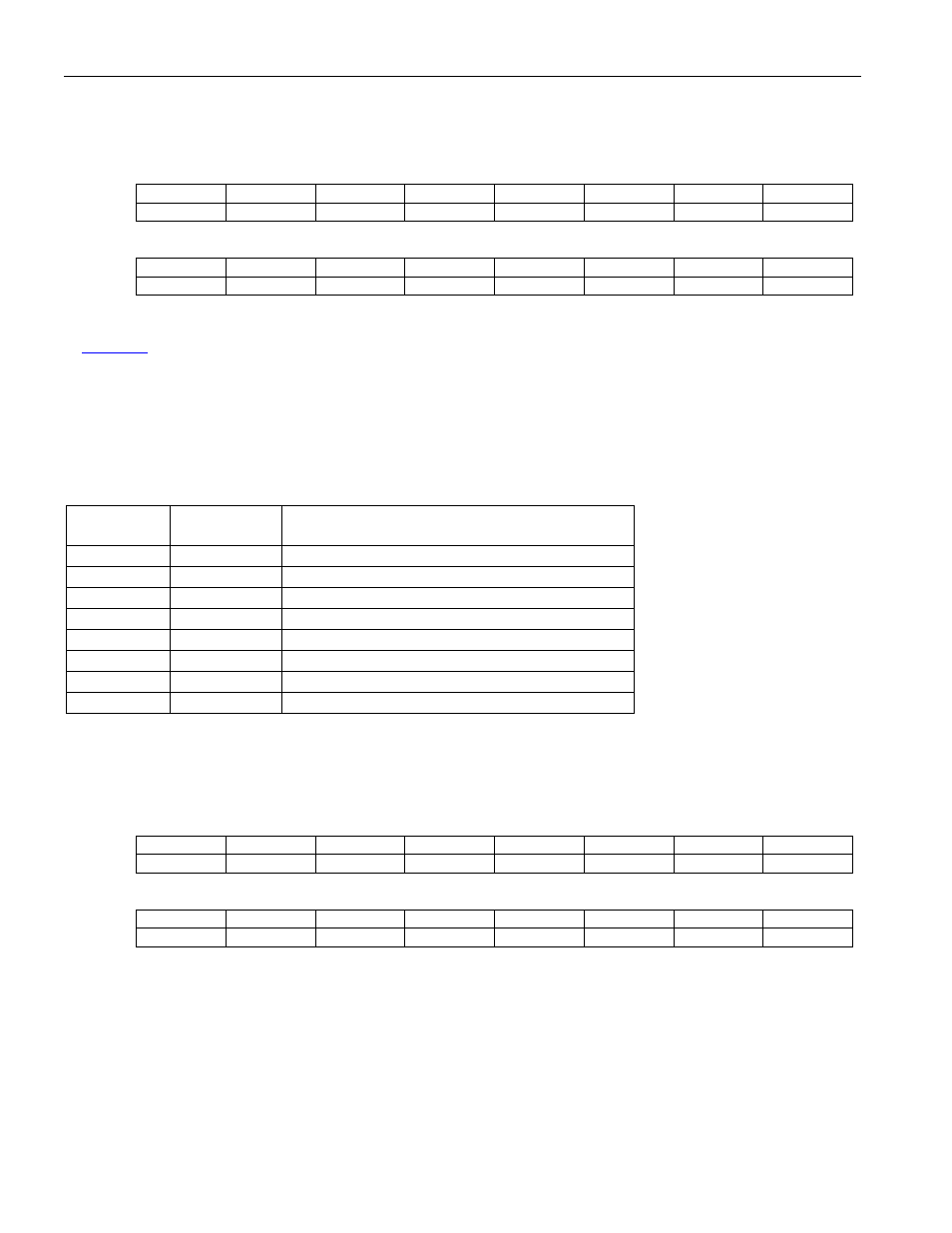

11.7.2 FEAC Receive Side Register Map

The receive side utilizes five registers.

Table 11-19. FEAC Receive Side Register Map

Address

Register

Register Description

0D0h FEAC.RCR

FEAC Receive Control Register

0D2h --

Unused

0D4h FEAC.RSR

FEAC Receive Status Register

0D6h FEAC.RSRL

FEAC Receive Status Register Latched

0D8h FEAC.RSRIE

FEAC Receive Status Register Interrupt Enable

0DAh --

Unused

0DCh FEAC.RFDR

FEAC Receive FIFO Data Register

0DEh --

Unused

11.7.2.1 Register Bit Descriptions

Register Name:

FEAC.RCR

Register Description:

FEAC Receive Control Register

Register Address:

0D0h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 1 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- -- -- -- --

RFR

Default

0 0 0 0 0 0 0 0

Bit 0: Receive FEAC Reset (RFR) –When 0, the Receive FEAC Processor and Receive FEAC FIFO will resume

normal operations. When 1, the Receive FEAC controller is reset. The FEAC FIFO is emptied, any transfer in

progress is halted, and all incoming data is discarded.