Hdlc.tfdr, Hdlc.tsr – Rainbow Electronics DS3170 User Manual

Page 157

DS3170 DS3/E3 Single-Chip Transceiver

157 of 233

Bit 1: Transmit FCS Processing Disable (TFPD) – This bit controls whether or not an FCS is calculated and

appended to the end of each packet. When 0, the calculated FCS bytes are appended to the end of the packet.

When 1, the packet is transmitted without an FCS.

Bit 0: Transmit FIFO Reset (TFRST) – When 0, the Transmit FIFO will resume normal operations, however, data

is discarded until a start of packet is received after RAM power-up is completed. When 1, the Transmit FIFO is

emptied, any transfer in progress is halted, the FIFO RAM is powered down, and all incoming data is discarded (all

TFDR register writes are ignored).

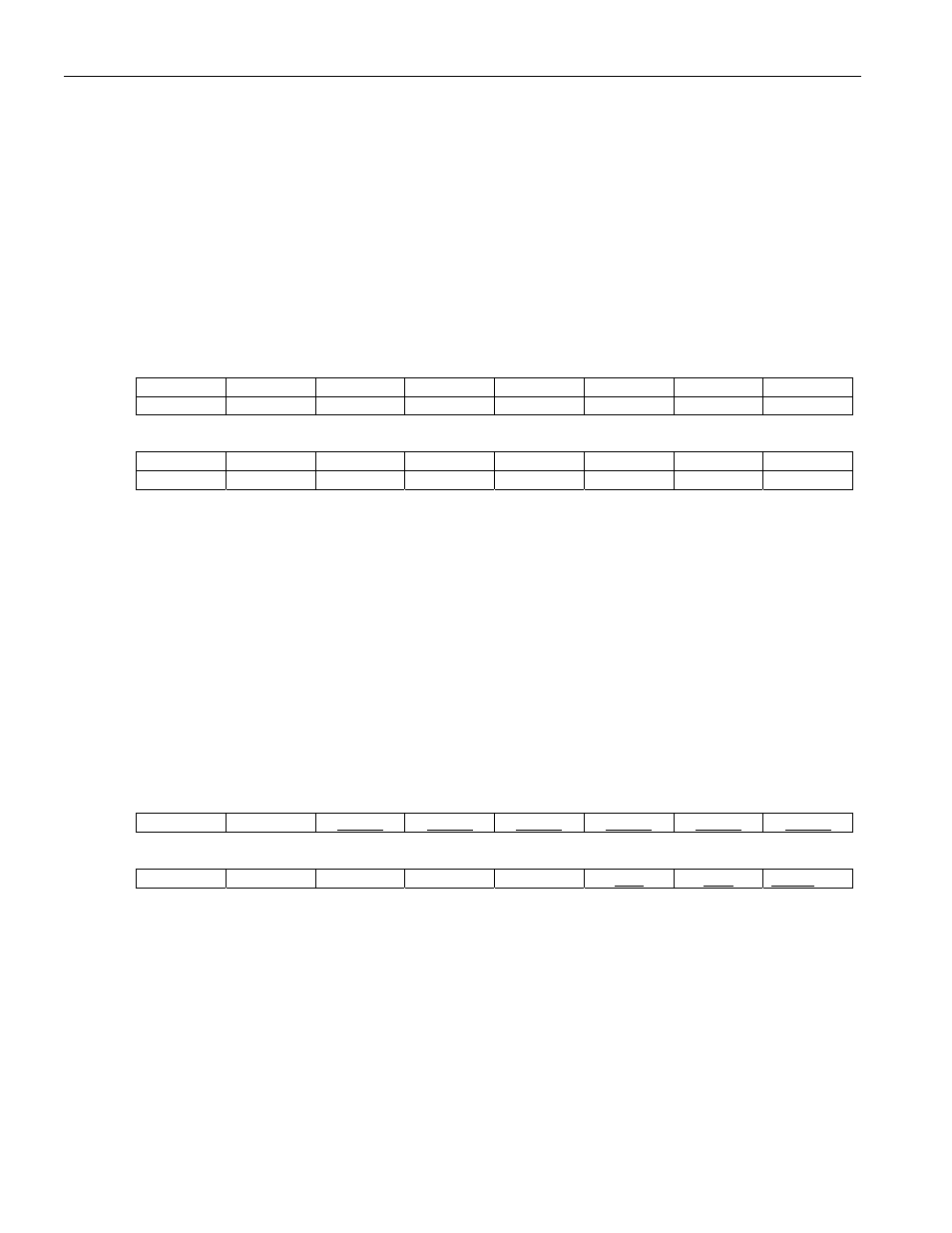

Register Name:

HDLC.TFDR

Register Description:

HDLC Transmit FIFO Data Register

Register Address:

0A2h

Bit

# 15 14 13 12 11 10 9 8

Name TFD7 TFD6 TFD5 TFD4 TFD3 TFD2 TFD1 TFD0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- -- -- -- --

TDPE

Default

0 0 0 0 0 0 0 0

Note: The FIFO data and status are loaded into the Transmit FIFO when the Transmit FIFO Data (TFD[7:0]) is

written (upper byte write). When read, the value of these bits is always zero.

Bits 15 to 8: Transmit FIFO Data (TFD[7:0]) – These eight bits are the packet data to be stored in the Transmit

FIFO. TFD[7] is the MSB, and TFD[0] is the LSB. If bit reordering is disabled, TFD[0] is the first bit transmitted, and

TFD[7] is the last bit transmitted. If bit reordering is enabled, TFD[7] is the first bit transmitted, and TFD[0] is the

last bit transmitted.

Bit 0: Transmit FIFO Data Packet End (TDPE) – When 0, the Transmit FIFO data is not a packet end. When 1,

the Transmit FIFO data is a packet end.

Register Name:

HDLC.TSR

Register Description:

HDLC Transmit Status Register

Register Address:

0A4h

Bit

# 15 14 13 12 11 10 9 8

Name -- -- TFFL5 TFFL4 TFFL3 TFFL2 TFFL1 TFFL0

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- -- --

TFF TFE THDA

Bits 13 to 8: Transmit FIFO Fill Level (TFFL[5:0]) – These six bits indicate the number of eight byte groups

available for storage (do not contain data) in the Transmit FIFO. E.g., a value of 21 (15h) indicates the FIFO has

168 (A8h) to 175 (AFh) bytes are available for storage.

Bit 2: Transmit FIFO Full (TFF) – When 0, the Transmit FIFO contains 255 or less bytes of data. When 1, the

Transmit FIFO is full.

Bit 1: Transmit FIFO Empty (TFE) – When 0, the Transmit FIFO contains at least one byte of data. When 1, the

Transmit FIFO is empty.

Bit 0: Transmit HDLC Data Storage Available (THDA) – When 0, the Transmit FIFO has less storage space

available in the Transmit FIFO than the Transmit HDLC data storage available level (TDAL[4:0]). When 1, the

Transmit FIFO has the same or more storage space available than the Transmit FIFO HDLC data storage available

level.