Bert.spr1, Bert.spr2, Bert.teicr – Rainbow Electronics DS3170 User Manual

Page 146

DS3170 DS3/E3 Single-Chip Transceiver

146 of 233

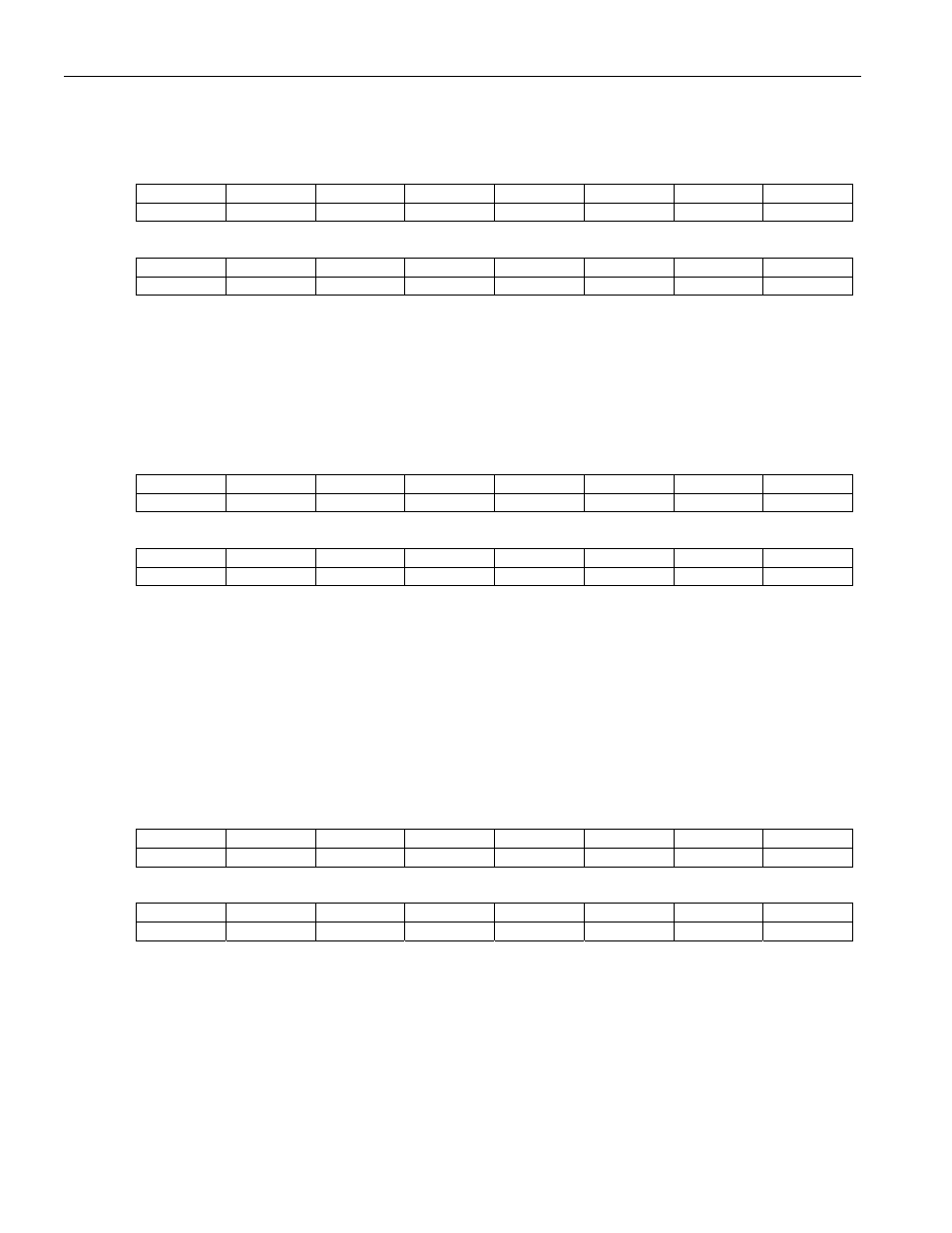

Register Name:

BERT.SPR1

Register Description:

BERT Seed/Pattern Register #1

Register Address:

064h

Bit

# 15 14 13 12 11 10 9 8

Name BSP15 BSP14 BSP13 BSP12 BSP11 BSP10 BSP9 BSP8

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name BSP7 BSP6 BSP5 BSP4 BSP3 BSP2 BSP1 BSP0

Default

0 0 0 0 0 0 0 0

Bits 15 to 0: BERT Seed/Pattern (BSP[15:0]) – Lower sixteen bits of 32 bits. Register description follows next

register.

Register Name:

BERT.SPR2

Register Description:

BERT Seed/Pattern Register #2

Register Address:

066h

Bit

# 15 14 13 12 11 10 9 8

Name BSP31 BSP30 BSP29 BSP28 BSP27 BSP26 BSP25 BSP24

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name BSP23 BSP22 BSP21 BSP20 BSP19 BSP18 BSP17 BSP16

Default

0 0 0 0 0 0 0 0

Bits 15 to 0: BERT Seed/Pattern (BSP[31:16]) - Upper 16 bits of 32 bits.

BERT Seed/Pattern (BSP[31:0]) – These 32 bits are the programmable seed for a transmit PRBS pattern, or the

programmable pattern for a transmit or receive repetitive pattern. BSP(31) will be the first bit output on the transmit

side for a 32-bit repetitive pattern or 32-bit length PRBS. BSP(31) will be the first bit input on the receive side for a

32-bit repetitive pattern.

Register Name:

BERT.TEICR

Register Description:

BERT Transmit Error Insertion Control Register

Register Address:

068h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

--

-- TEIR2 TEIR1 TEIR0 BEI TSEI MEIMS

Default

0 0 0 0 0 0 0 0

Bits 5 to 3: Transmit Error Insertion Rate (TEIR[2:0]) – These three bits indicate the rate at which errors are

inserted in the output data stream. One out of every 10

n

bits is inverted. TEIR[2:0] is the value n. A TEIR[2:0] value

of 0 disables error insertion at a specific rate. A TEIR[2:0] value of 1 result in every 10

th

bit being inverted. A

TEIR[2:0] value of 2 result in every 100

th

bit being inverted. Error insertion starts when this register is written to with

a TEIR[2:0] value that is nonzero. If this register is written to during the middle of an error insertion process, the

new error rate will be started after the next error is inserted.