T3.rsrl1, T3.rsrl2 – Rainbow Electronics DS3170 User Manual

Page 179

DS3170 DS3/E3 Single-Chip Transceiver

179 of 233

Register Name:

T3.RSRL1

Register Description:

T3 Receive Status Register Latched #1

Register Address:

128h

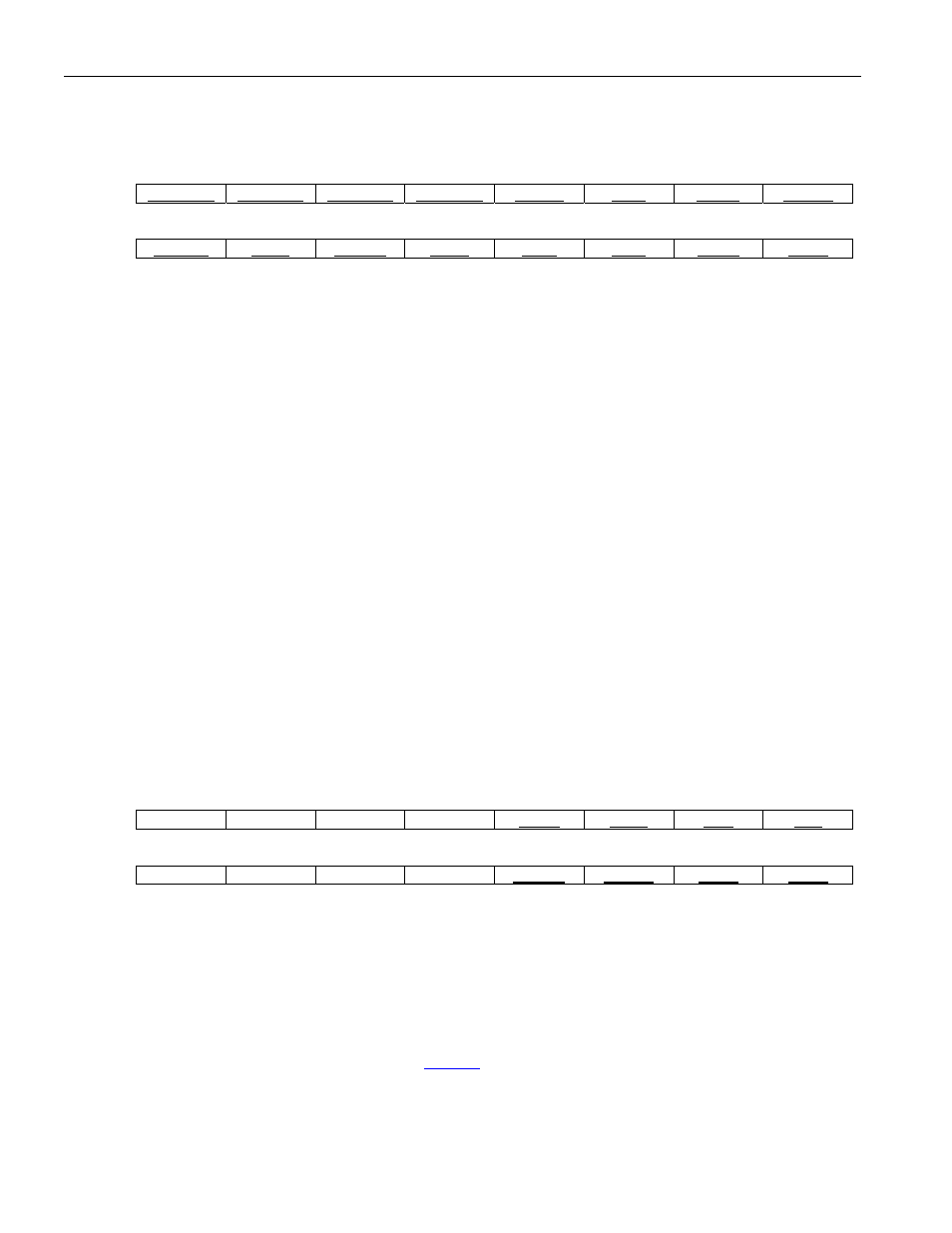

Bit

# 15 14 13 12 11 10 9 8

Name Reserved Reserved Reserved Reserved T3FML AICL IDLEL RUA1L

Bit

# 7 6 5 4 3 2 1 0

Name OOMFL SEFL COFAL LOFL RAIL AISL OOFL LOSL

Bit 11: T3 Framing Format Mismatch Latched (T3FML) – This bit is set when the T3FM bit transitions from zero

to one.

Bit 10: Application Identification Channel Change Latched (AICL) – This bit is set when the AIC bit changes

state.

Bit 9: DS3 Idle Signal Change Latched (IDLEL) – This bit is set when the IDLE bit changes state.

Bit 8: Receive Unframed All 1’s Change Latched (RUA1L) – This bit is set when the RUA1 bit changes state.

Bit 7: Out Of MultiFrame Change Latched (OOMFL) – This bit is set when the OOMF bit changes state.

Bit 6: Severely Errored Frame Change Latched (SEFL) – This bit is set when the SEF bit changes state.

Bit 5: Change Of Frame Alignment Latched (COFAL) – This bit is set when the data path frame counters are

updated with a new DS3 frame alignment that is different from the previous DS3 frame alignment.

Bit 4: Loss Of Frame Change Latched (LOFL) – This bit is set when the LOF bit changes state.

Bit 3: Remote Defect Indication Change Latched (RDIL) – This bit is set when the RDI bit changes state.

Bit 2: Alarm Indication Signal Change Latched (AISL) – This bit is set when the AIS bit changes state.

Bit 1: Out Of Frame Change Latched (OOFL) – This bit is set when the OOF bit changes state.

Bit 0: Loss Of Signal Change Latched (LOSL) – This bit is set when the LOS bit changes state.

Register Name:

T3.RSRL2

Register Description:

T3 Receive Status Register Latched #2

Register Address:

12Ah

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- --

CPEL FBEL PEL FEL

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- --

CPECL FBECL PECL FECL

Bit 11: C-bit Parity Error Latched (CPEL) – This bit is set when a C-bit parity error is detected. This bit is set to

zero in M23 DS3 mode.

Bit 10: Remote Error Indication Latched (FBEL) – This bit is set when a far-end block error is detected. This bit

is set to zero in M23 DS3 mode.

Bit 9: P-bit Parity Error Latched (PEL) – This bit is set when a P-bit parity error is detected.

Bit 8: Framing Error Latched (FEL) – This bit is set when a framing error is detected. The type of framing error

event that causes this bit to be set is determined by

.FECC[1:0]

Bit 3: C-bit Parity Error Count Latched (CPECL) – This bit is set when the CPEC bit transitions from zero to one.

This bit is set to zero in M23 DS3 mode.