Bert, Bert register map, Bert register bit descriptions – Rainbow Electronics DS3170 User Manual

Page 144: Table 11-13. bert register map, Bert.cr

DS3170 DS3/E3 Single-Chip Transceiver

144 of 233

11.4 BERT

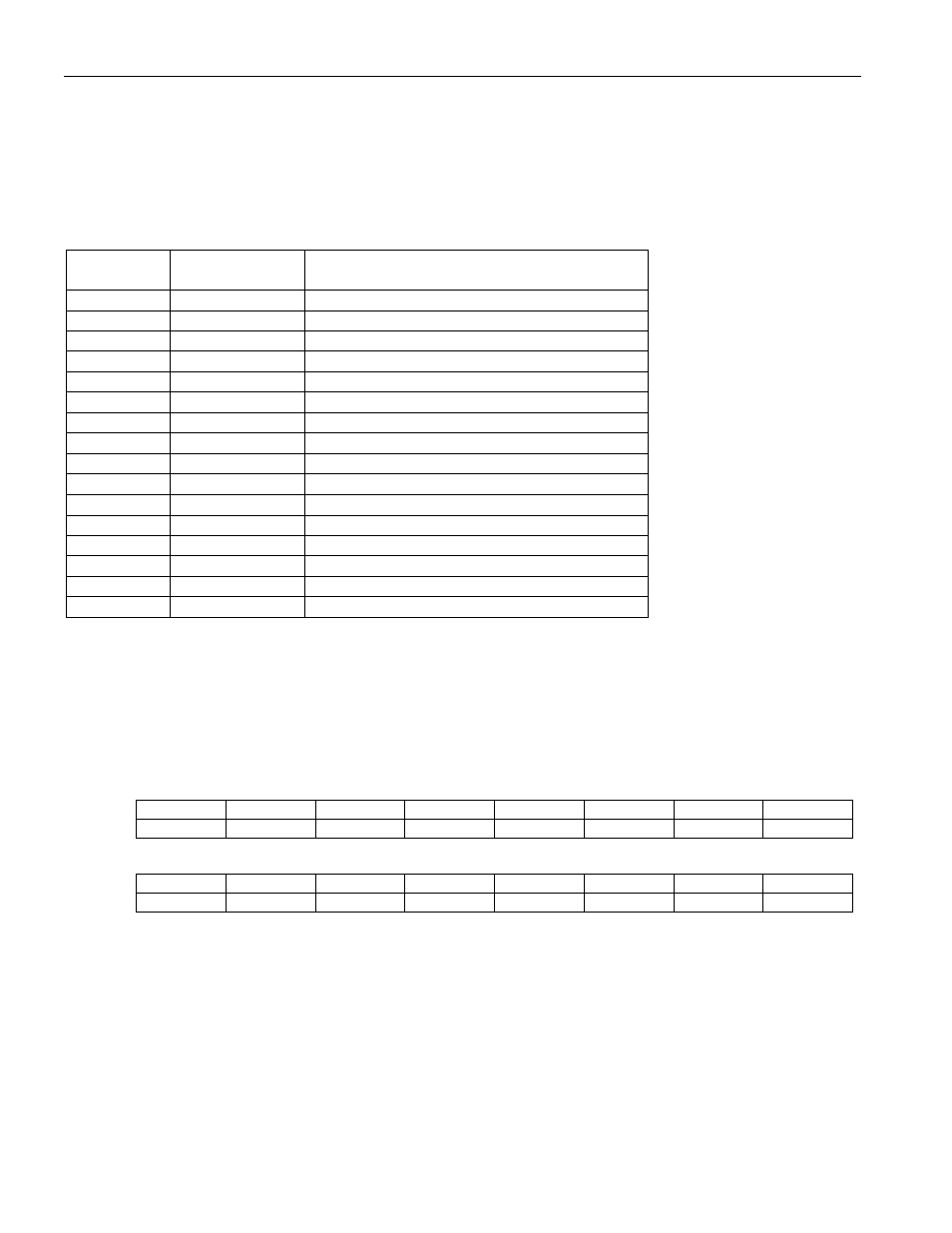

11.4.1 BERT Register Map

The BERT utilizes twelve registers.

Table 11-13. BERT Register Map

Address

Register

Register Description

060h

BERT.CR

BERT Control Register

062h

BERT.PCR

BERT Pattern Configuration Register

064h

BERT.SPR1

BERT Seed/Pattern Register #1

066h

BERT.SPR2

BERT Seed/Pattern Register #2

068h

BERT.TEICR

BERT Transmit Error Insertion Control Register

06Ah

--

Unused

06Ch

BERT.SR

BERT Status Register

06Eh

BERT.SRL

BERT Status Register Latched

070h

BERT.SRIE

BERT Status Register Interrupt Enable

072h

--

Unused

074h

BERT.RBECR1

BERT Receive Bit Error Count Register #1

076h

BERT.RBECR2

BERT Receive Bit Error Count Register #2

078h

BERT.RBCR1

BERT Receive Bit Count Register #1

07Ah

BERT.RBCR2

BERT Receive Bit Count Register #2

07Ch

--

Unused

07Eh

--

Unused

11.4.2 BERT Register Bit Descriptions

Register Name:

BERT.CR

Register Description:

BERT Control Register

Register Address:

060h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name PMUM LPMU RNPL RPIC MPR APRD TNPL TPIC

Default

0 0 0 0 0 0 0 0

Bit 7: Performance Monitoring Update Mode (PMUM) – When 0, a performance monitoring update is initiated by

the LPMU register bit. When 1, a performance monitoring update is initiated by the global or port PMU register bit.

Note: If the LPMU bit or the global or port PMU bit is one, changing the state of this bit may cause a performance

monitoring update to occur.

Bit 6: Local Performance Monitoring Update (LPMU) – This bit causes a performance monitoring update to be

initiated if local performance monitoring update is enabled (PMUM = 0). A 0 to 1 transition causes the performance

monitoring registers to be updated with the latest data, and the counters reset (0 or 1). For a second performance

monitoring update to be initiated, this bit must be set to 0, and back to 1. If LPMU goes low before the PMS bit

goes high; an update might not be performed. This bit has no affect when PMUM=1.

Bit 5: Receive New Pattern Load (RNPL) – A zero to one transition of this bit will cause the programmed test

pattern (QRSS, PTS, PLF[4:0}, PTF[4:0], and BSP[31:0]) to be loaded in to the receive pattern generator. This bit