T3.rsrie1 – Rainbow Electronics DS3170 User Manual

Page 180

DS3170 DS3/E3 Single-Chip Transceiver

180 of 233

Bit 2: Remote Error Indication Count Latched (FBECL) – This bit is set when the FBEC bit transitions from zero

to one. This bit is set to zero in M23 DS3 mode.

Bit 1: P-bit Parity Error Count Latched (PECL) – This bit is set when the PEC bit transitions from zero to one.

Bit 0: Framing Error Count Latched (FECL) – This bit is set when the FEC bit transitions from zero to one.

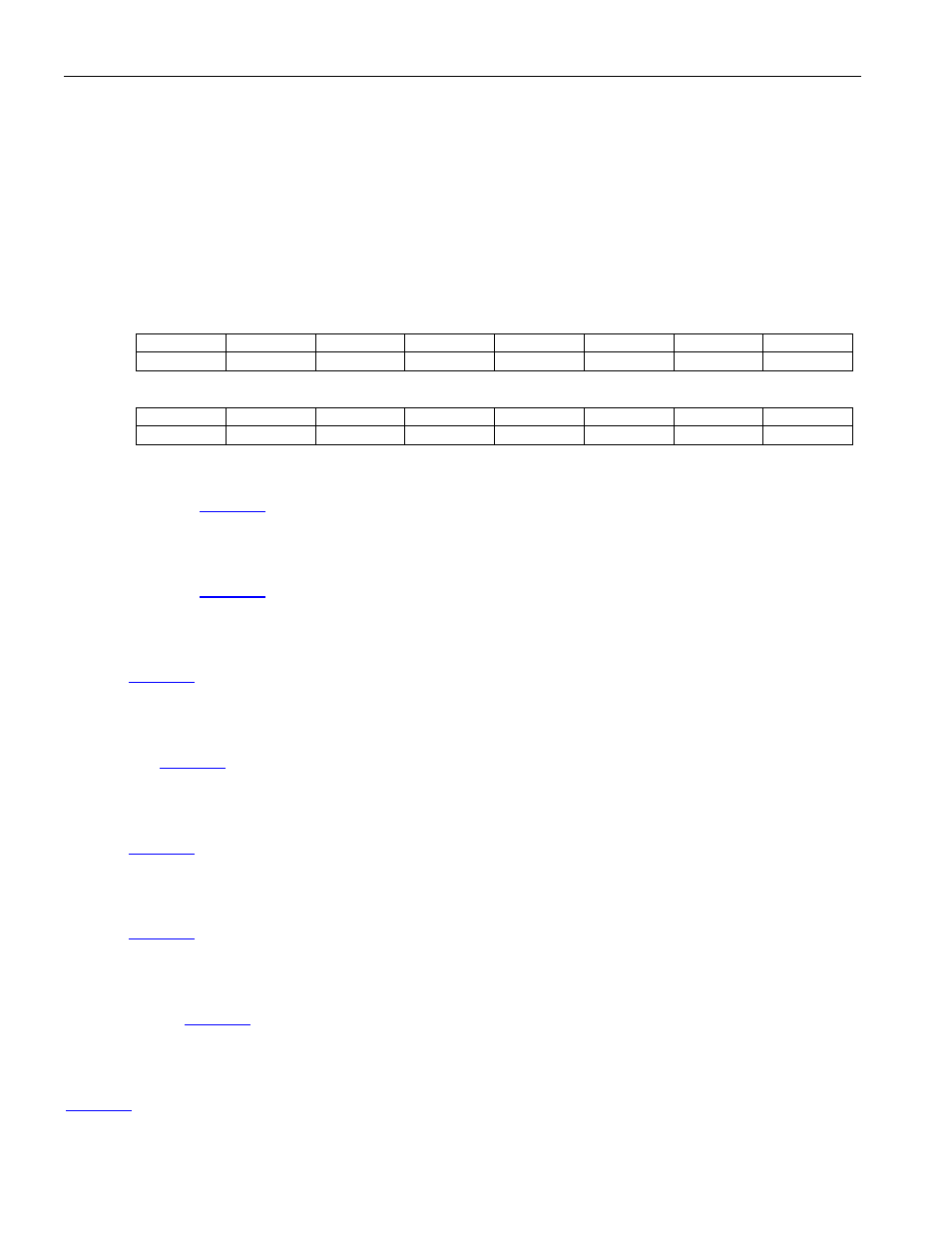

Register Name:

T3.RSRIE1

Register Description:

T3 Receive Status Register Interrupt Enable #1

Register Address:

12Ch

Bit

# 15 14 13 12 11 10 9 8

Name Reserved Reserved Reserved Reserved T3FMIE AICIE IDLEIE RUA1IE

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name OOMFIE SEFIE COFAIE LOFIE RAIIE AISIE OOFIE LOSIE

Default

0 0 0 0 0 0 0 0

Bit 11: T3 Framing Format Mismatch Interrupt Enable (T3FMIE) – This bit enables an interrupt if the T3FML bit

is set and the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 10: Application Identification Channel Interrupt Enable (AICIE) – This bit enables an interrupt if the AICL bit

is set and the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 9: DS3 Idle Signal Change Interrupt Enable (IDLEIE) – This bit enables an interrupt if the IDLEL bit is set and

the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 8: Receive Unframed All 1’s Interrupt Enable (RUA1IE) – This bit enables an interrupt if the RUA1L bit is set

and the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 7: Out Of Multiframe Interrupt Enable (OOMFIE) – This bit enables an interrupt if the OOMFL bit is set and

the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 6: Severely Errored Frame Interrupt Enable (SEFIE) – This bit enables an interrupt if the SEFL bit is set and

the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 5: Change Of Frame Alignment Interrupt Enable (COFAIE) – This bit enables an interrupt if the COFAL bit is

set and the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 4: Loss Of Frame Interrupt Enable (LOFIE) – This bit enables an interrupt if the LOFL bit is set and the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled