Gl.srl, Gl.sr – Rainbow Electronics DS3170 User Manual

Page 131

DS3170 DS3/E3 Single-Chip Transceiver

131 of 233

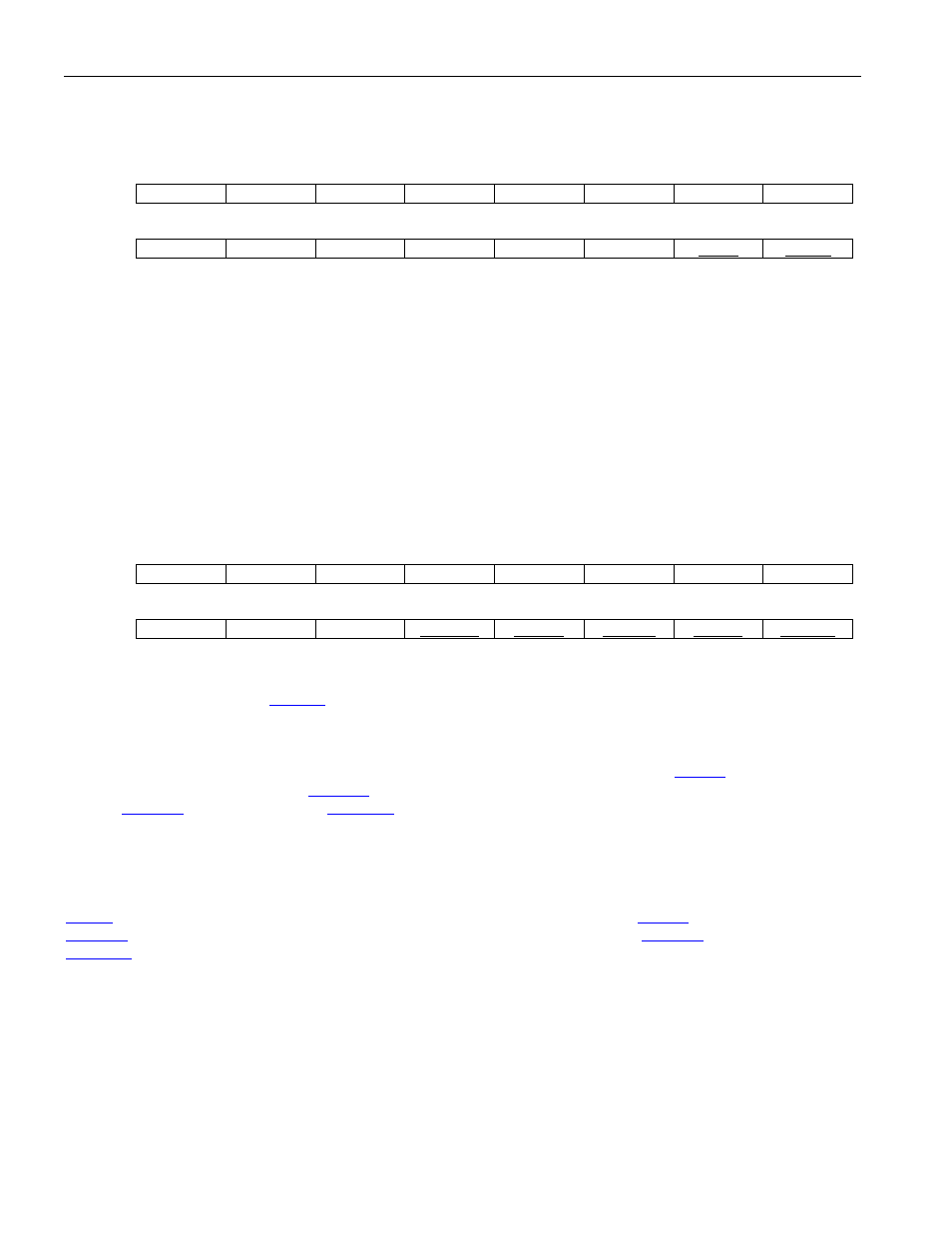

Register Name:

GL.SR

Register Description:

Global Status Register

Register Address:

014h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- -- -- --

CLOL GPMS

Bit 1 : CLAD Loss of Lock (CLOL) – This bit is set when any of the PLLs in the CLAD are not locked to the

reference frequency.

Bit 0: Global Performance Monitoring Update Status (GPMS) This bit is set when all of the port performance

register update status bits (PORT.SR.PMU), that are enabled for global update control (PORT.CR2.PMUM=1), are

set. It is an “AND” of all the globally enabled port PMU status bits. In global software update mode, the global

update request bit (GL.CR.GPMU) should be held high until this status bit goes high.

0 = The associated update request signal is low or not all register updates are completed

1 = The requested performance register updates are all completed

Register Name:

GL.SRL

Register Description:

Global Status Register Latched

Register Address:

016h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- --

8KREFL CLADL ONESL CLOLL GPMSL

Bit 4: 8kHz Reference Activity Status Latched (8KREFL) This bit will be set when the 8 kHz reference signal on

the GPIO4 pin is active. The

.G8KIS bit must be set for the activity to be monitored.

Bit 3: CLAD Reference Clock Activity Status Latched (CLADL) This bit will be set when the CLAD PLL

reference clock signal on the REFCLK pin is active.

Bit 2: One Second Status Latched (ONESL) This bit will be set once a second. The

.GSR status bit will

be set when this bit is set and the

.ONESIE bit is enabled. The

INT pin will be driven low if this bit is set

and the

.ONESIE bit and the

.GSRIE bit are enabled.

Bit 1: CLAD Loss Of Lock Latched (CLOLL) This bit will be set when the GL.SR.CLOL status bit changes from

low to high. The GL.ISR.GSR bit will be set when this bit is set and the GL.SRIE.CLOLIE bit is set and the

INT pin

will be driven low if the GL.ISRIE.GSRIE bit is also enabled.

Bit 0: Global Performance Monitoring Update Status Latched (GPMSL) This bit will be set when the

.GPMS status bit changes from low to high. This bit will set the

.GSR status bit if the

.GPMSIE is enabled. This bit will drive the interrupt pin low if the

.GPMSIE bit and the

.GSRIE bit are enabled.