Performance monitor counter update details, Table 9-16. gpio port alarm monitor select, Table 9-16 – Rainbow Electronics DS3170 User Manual

Page 69

DS3170 DS3/E3 Single-Chip Transceiver

69 of 233

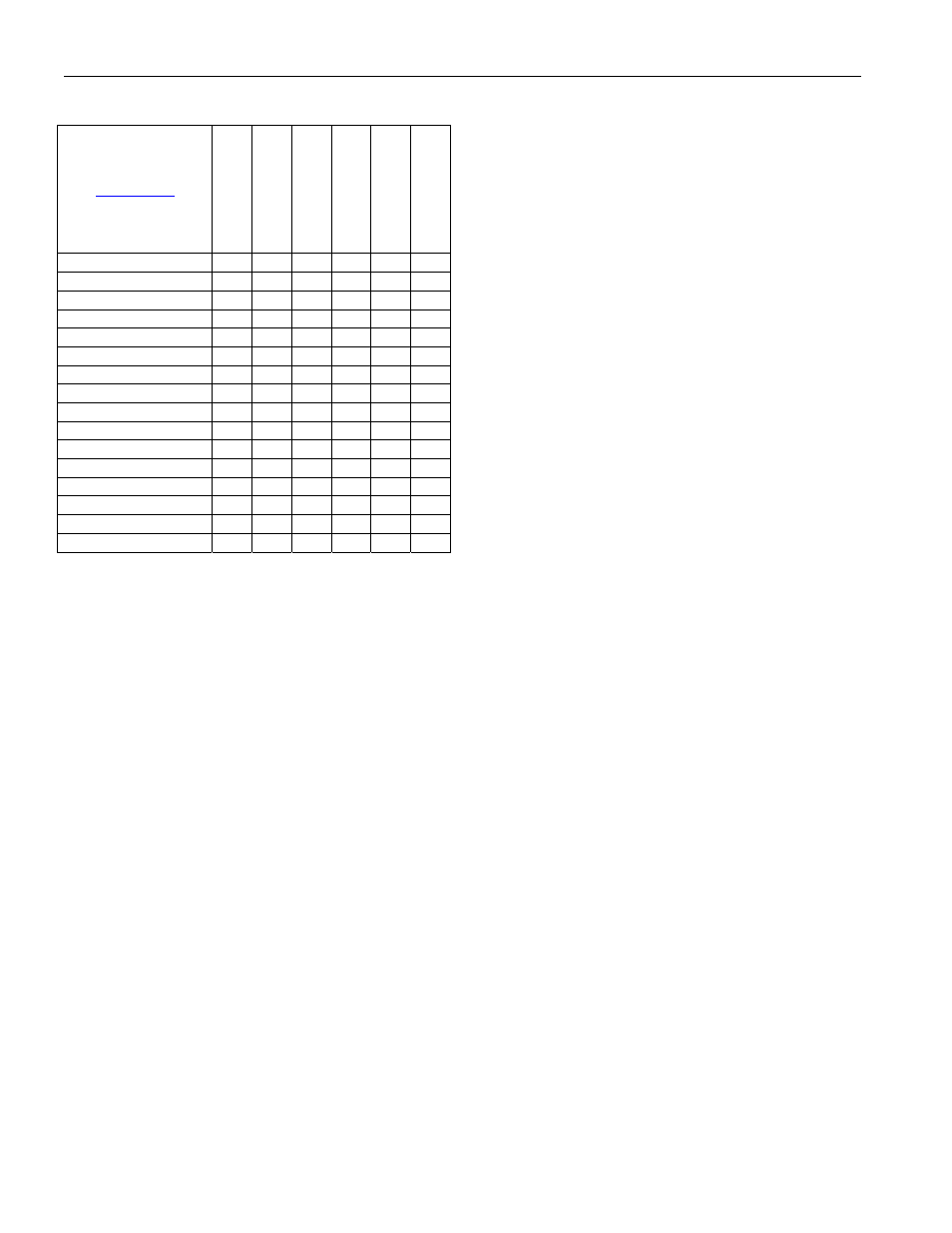

Table 9-16. GPIO Port Alarm Monitor Select

GPIO(A/B)[3:0]

LINE

LOS

DS

3/

E

3 OOF

DS

3/

E

3 LOF

DS3/

E3 AIS

DS3/

E3 RAI

DS3 I

D

LE

0000

X

0001

X

0010

X

0011

X

0100

X

0101

X

0110

0111

1000

1001

1010

1011

X X X

1100

1101

X X X

1110

X

X

1111

X X X X X X

9.4.5 Performance Monitor Counter Update Details

The performance monitor counters are designed to count at least one second of events before saturating to the

maximum count. There is a status bit associated with some of the performance monitor counters that is set when

the its counter is greater than zero, and a latched status bit that gets set when the counter changes from zero to

one. There is also a latched status bit that gets set on every event that causes the error counter to increment.

There is a read register for each performance monitor counter. The count value of the counter gets loaded into this

register and the counter is cleared when the update-clear operation is performed. If there is an event to be counted

at the exact moment (clock cycle) that the counter is to be cleared then the counter will be set to a value of one so

that that event will be counted.

The Performance Monitor Update signal affects the counter registers of the following blocks: the BERT, the DS3/E3

framer, the Line Encoder/Decoder.

The update-clear operation is controlled by the Performance Monitor Update signal (PMU). The update-clear

operation will update the error counter registers with the value of the error counter and also reset each counter.

The PMU signal can be created in hardware or software. The hardware sources can come from the one second

counter or one of the general-purpose IO pins, which can be programmed to source this signal. The software

sources can come from one of the port control register bits or one of the global control register bits. When using the

software update method, the PMU control bit should be set to initiate the process and when the PMS status bit gets

set, the PMU control bit should be cleared making it ready for the next update. When using the hardware update

method, the PMS bit will be set shortly after the hardware signal goes high, and cleared shortly after the hardware

signal goes low. The latched PMS signal can be used to generate an interrupt for reading the count registers. If the

port is not configured for global PMU signals, the PMS signal from that port should be blocked from affecting the

global PMS status.