Register bit descriptions, Tt.rcr, Tt.rtiar – Rainbow Electronics DS3170 User Manual

Page 170

DS3170 DS3/E3 Single-Chip Transceiver

170 of 233

11.8.2.1 Register Bit Descriptions

Register Name:

TT.RCR

Register Description:

Trail Trace Receive Control Register

Register Address:

0F0h

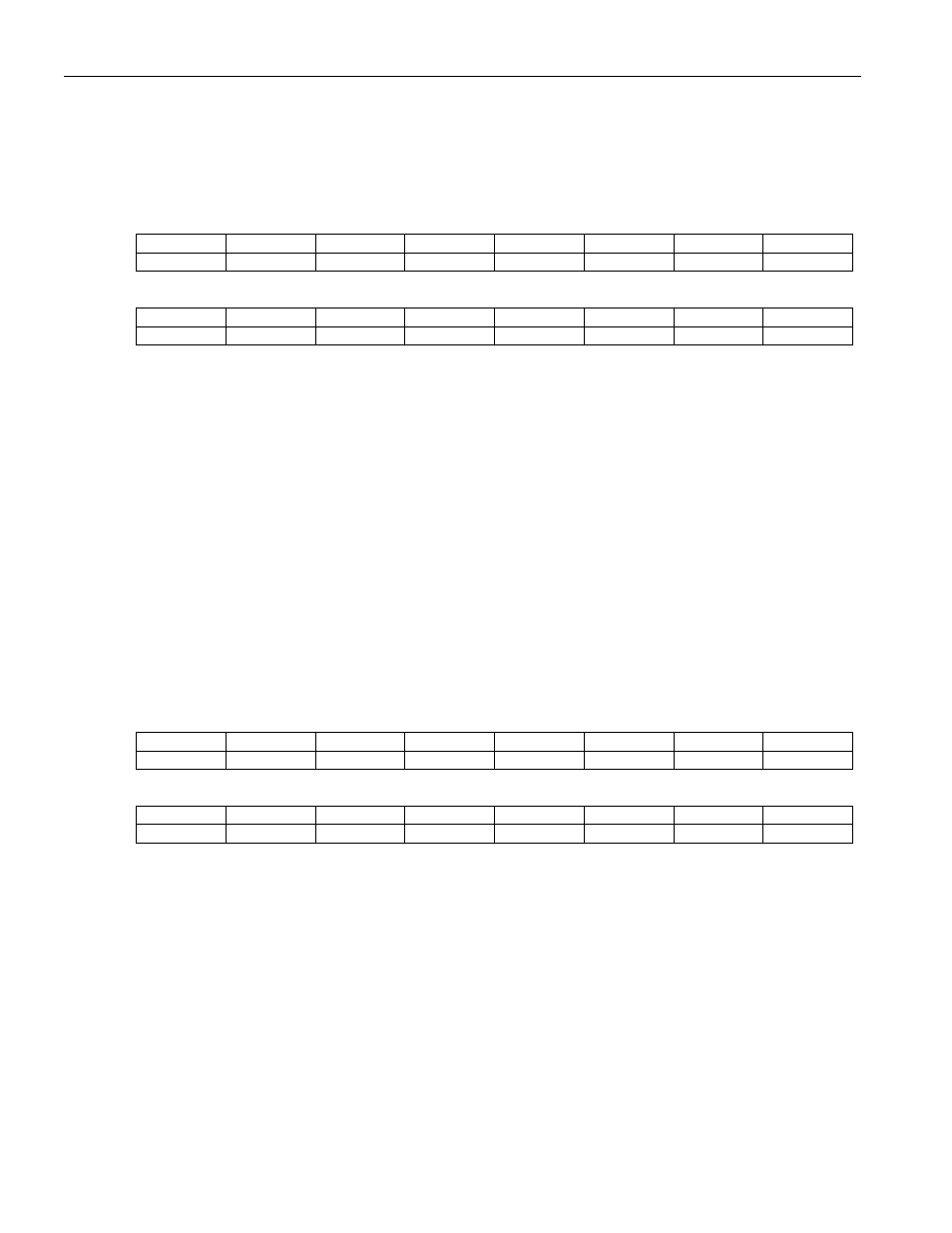

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name -- --

Reserved

Reserved

RMAD

RETCE

RDIE

RBRE

Default

0 0 0 0 0 0 0 0

Bit 3: Receive Multiframe Alignment Disable (RMAD) – When 0, multiframe alignment is performed. When 1,

multiframe alignment is disabled and the trail trace bytes are stored starting with a random byte.

Bit 2: Receive Expected Trail Trace Comparison Enable (RETCE) – When 0, expected trail trace comparison is

disabled. When 1, expected trail trace comparison is performed. Note: When the RMAD bit is one, expected trail

trace comparison is disabled regardless of the setting of this bit.

Bit 1: Receive Data Inversion Enable (RDIE) – When 0, the incoming data is directly passed on for trail trace

processing. When 1, the incoming data is inverted before being passed on for trail trace processing.

Bit 0: Receive Bit Reordering Enable (RBRE) – When 0, bit reordering is disabled (The first bit received is the

MSB TT.RIR.RTD[7] of the byte). When 1, bit reordering is enabled (The first bit received is the LSB

TT.RIR.RTD[0] of the byte).

Register Name:

TT.RTIAR

Register Description:

Trail Trace Receive Identifier Address Register

Register Address:

0F2h

Bit

# 15 14 13 12 11 10 9 8

Name

--

-- Reserved

Reserved

ETIA3 ETIA2 ETIA1 ETIA0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name -- --

Reserved

Reserved

RTIA3 RTIA2 RTIA1 RTIA0

Default

0 0 0 0 0 0 0 0

Bits 11 to 8: Expected Trail Trace Identifier Address (ETIA[3:0]) – These four bits indicate the expected trail

trace identifier byte to be read/written by the next memory access. Address 0h indicates the first byte of the

expected trail trace identifier. Note: The value of these bits increments with each expected trail trace identifier

memory access (when these bits are Fh, a memory access will return them to 0h).

Bits 3 to 0: Receive Trail Trace Identifier Address (RTIA[3:0]) – These four bits indicate the receive trail trace

identifier byte to be read by the next memory access. Address 0h indicates the first byte of the receive trail trace

identifier. Note: The value of these bits increments with each received trail trace identifier memory access (when

these bits are Fh, a memory access will return them to 0h).