Hdlc, Hdlc transmit side register map, Register bit descriptions – Rainbow Electronics DS3170 User Manual

Page 156: Table 11-16. transmit side hdlc register map, Hdlc.tcr

DS3170 DS3/E3 Single-Chip Transceiver

156 of 233

11.6 HDLC

11.6.1 HDLC Transmit Side Register Map

The transmit side utilizes five registers.

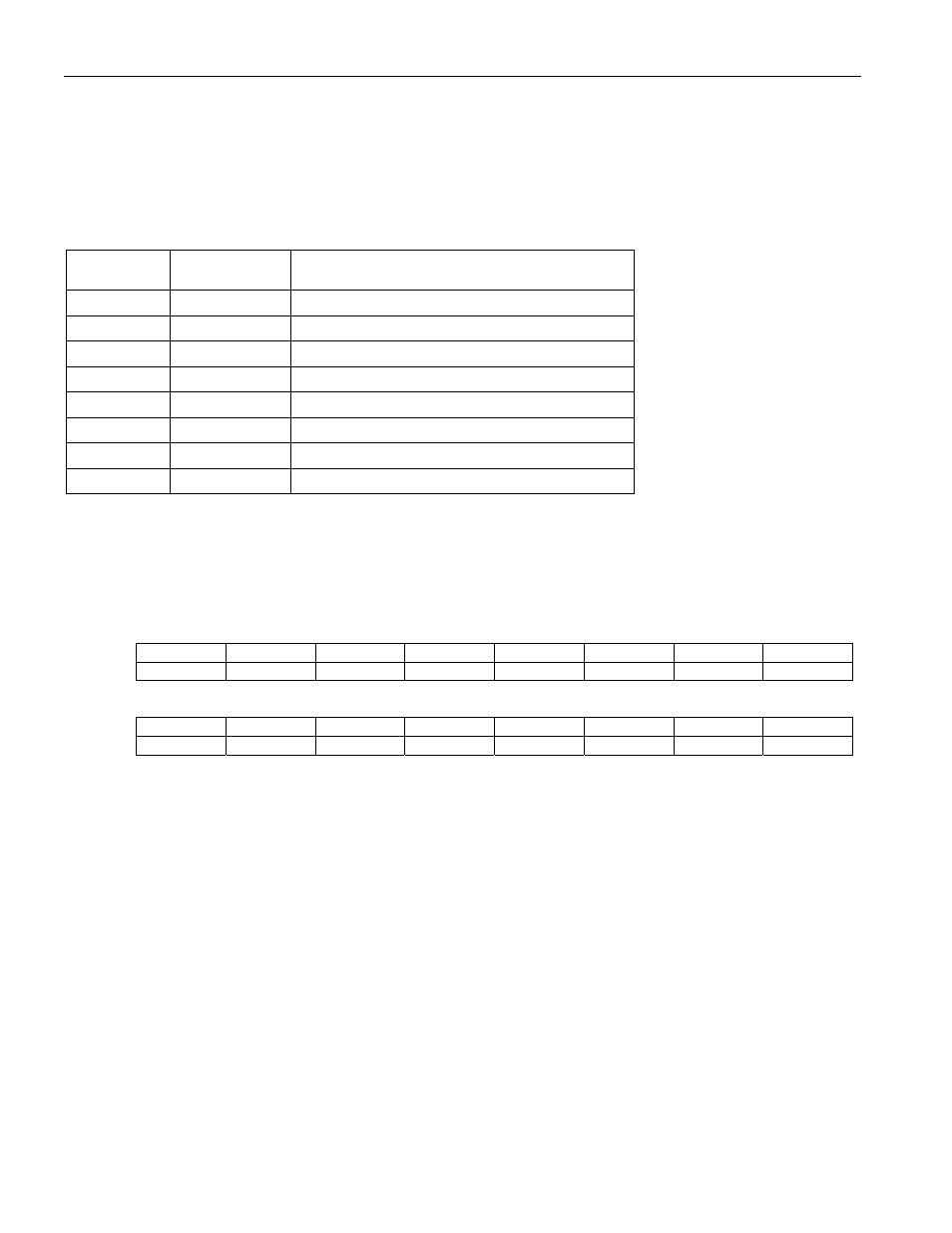

Table 11-16. Transmit Side HDLC Register Map

Address

Register

Register Description

0A0h HDLC.TCR

HDLC Transmit Control Register

0A2h HDLC.TFDR

HDLC Transmit FIFO Data Register

0A4h HDLC.TSR

HDLC Transmit Status Register

0A6h HDLC.TSRL

HDLC Transmit Status Register Latched

0A8h HDLC.TSRIE

HDLC Transmit Status Register Interrupt Enable

0AAh --

Unused

0ACh --

Unused

0AEh --

Unused

11.6.1.1 Register Bit Descriptions

Register Name:

HDLC.TCR

Register Description:

HDLC Transmit Control Register

Register Address:

0A0h

Bit

# 15 14 13 12 11 10 9 8

Name

--

--

--

TDAL4 TDAL3 TDAL2 TDAL1 TDAL0

Default

0 0 0 0 1 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name -- TPSD

TFEI

TIFV

TBRE

TDIE

TFPD

TFRST

Default

0 0 0 0 0 0 0 0

Bits 12 to 8: Transmit HDLC Data Storage Available Level (TDAL[4:0]) – These five bits indicate the minimum

number of bytes ([TDAL*8}+1) that must be available for storage (do not contain data) in the Transmit FIFO for

HDLC data storage to be available. For example, a value of 21 (15h) results in HDLC data storage being available

(THDA=1) when the Transmit FIFO has 169 (A9h) bytes or more available for storage, and HDLC data storage not

being available (THDA=0) when the Transmit FIFO has 168 (A8h) bytes or less available for storage.

Bit 6: Transmit Packet Start Disable (TPSD) – When 0, the Transmit Packet Processor will continue sending

packets after the current packet end. When 1, the Transmit Packet Processor will stop sending packets after the

current packet end.

Bit 5: Transmit FCS Error Insertion (TFEI) – When 0, the calculated FCS (inverted CRC-16) is appended to the

packet. When 1, the inverse of the calculated FCS (noninverted CRC-16) is appended to the packet causing an

FCS error. This bit is ignored if transmit FCS processing is disabled (TFPD = 1).

Bit 4: Transmit Inter-frame Fill Value (TIFV) – When 0, inter-frame fill is done with the flag sequence (7Eh).

When 1, inter-frame fill is done with all ‘1’s.

Bit 3: Transmit Bit Reordering Enable (TBRE) – When 0, bit reordering is disabled (The first bit transmitted is the

LSB of the Transmit FIFO Data byte TFD[0]). When 1, bit reordering is enabled (The first bit transmitted is the MSB

of the Transmit FIFO Data byte TFD[7]).

Bit 2: Transmit Data Inversion Enable (TDIE) – When 0, the outgoing data is directly output from packet

processing. When 1, the outgoing data is inverted before being output from packet processing.