Rainbow Electronics DS3170 User Manual

Page 31

DS3170 DS3/E3 Single-Chip Transceiver

31 of 233

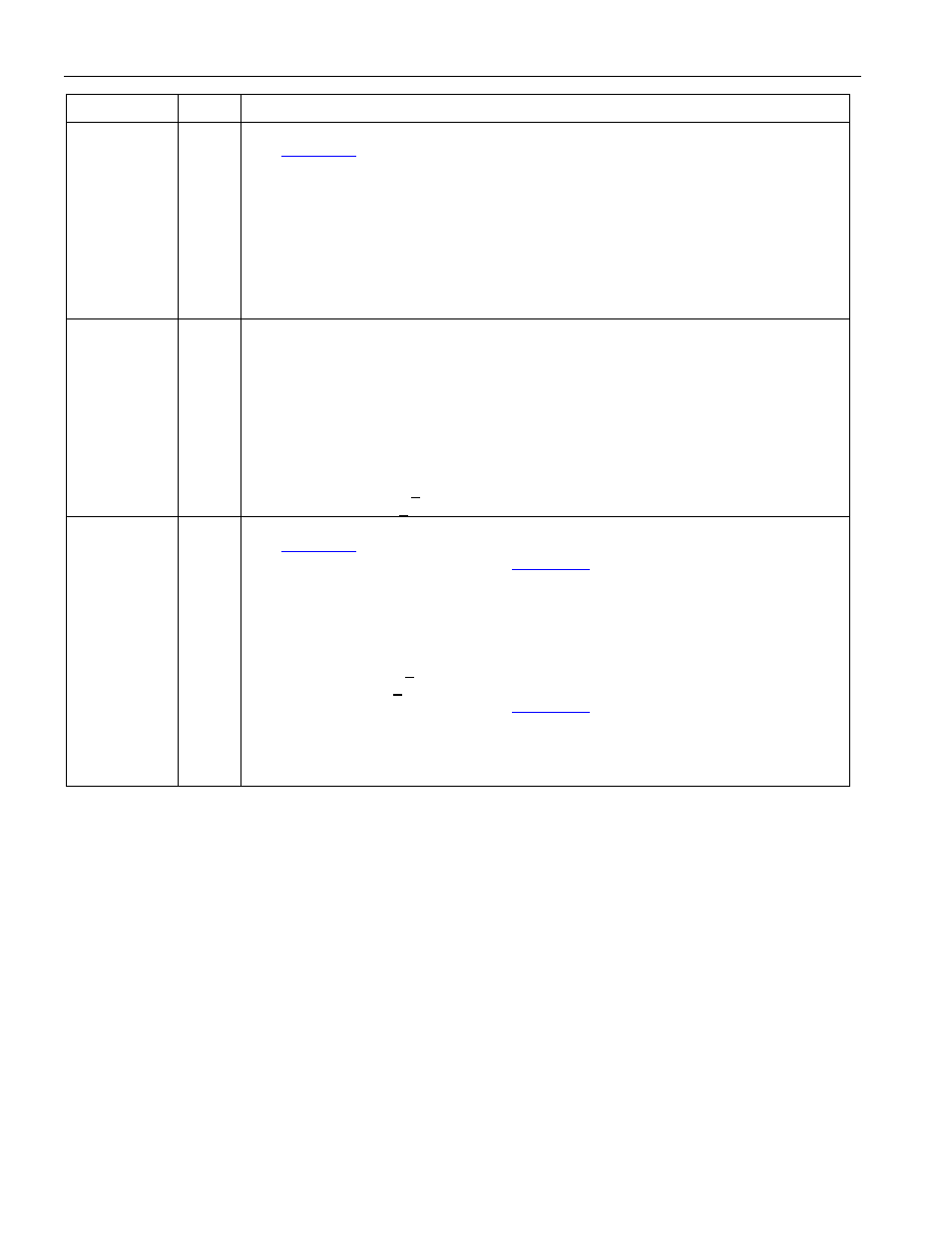

PIN NAME

TYPE

PIN DESCRIPTION

TSOFI

I

Transmit Start Of Frame Input

See

TSOFI: This signal can be used to align the start of the DS3 or E3 frames on the

TSER pin to an external signal. In framed modes, the TSOFI signal can be used to

align the start of frame signal position on the TSER/TOH pin to the rising edge of a

signal on this pin. The signal edge does not need to occur on every frame and can be

tied high or low. The signal is sampled on the positive clock edge of the referenced

clock pin if the clock pin signal is not inverted, otherwise it is sampled on the falling

edge of the clock. The signal is typically referenced to the TCLKI transmit clock input

pins, but it can be referenced to the TLCLK, TCLKO, RCLKO and RLCLK clock pins.

This signal can be inverted.

TSER

I

Transmit Serial Data

TSER: When the port framer is configured for either the DS3 or E3 framed modes,

this pin is used as the source of the DS3/E3 payload data. When the port is

configured for a clear channel mode, this pin is used as the source of the DS3/E3

data signal. The signal is sampled on the positive clock edge of the referenced clock

pin if the clock pin signal is not inverted, otherwise it is sampled on the falling edge of

the clock. The signal is typically referenced to the TCLKI transmit clock input pins, but

it can be referenced to the TLCLK, TCLKO / TGCLK, RCLKO and RLCLK clock pins

This signal can be inverted.

o DS3: 44.736 Mbps +20ppm

o E3: 34.368 Mbps +20ppm

TCLKO /

TGCLK

O

Transmit Clock Output / Gapped Clock

See

TCLKO: When TCLKO is selected by

.TCLKS, this clock output is

enabled. This clock is the same clock as the internal framer transmit clock. This clock

is typically used for the reference clock for the TSOFI, TSER, and TSOFO / TDEN

signals but can also be used as the reference for the TPOS / TDAT and TNEG

signals.

This signal can be inverted.

o DS3: 44.736 MHz +20 ppm

o E3: 34.368 MHz +20 ppm

TGCLK: When TGCLK is selected by

.TCLKS, this gated output clock is

enabled. This gapped clock is the same clock as the internal framer transmit clock

and is gated by TDEN. This clock is typically used for the reference clock for the

TSER signal.

This signal can be inverted.