Rainbow Electronics DS3170 User Manual

Page 33

DS3170 DS3/E3 Single-Chip Transceiver

33 of 233

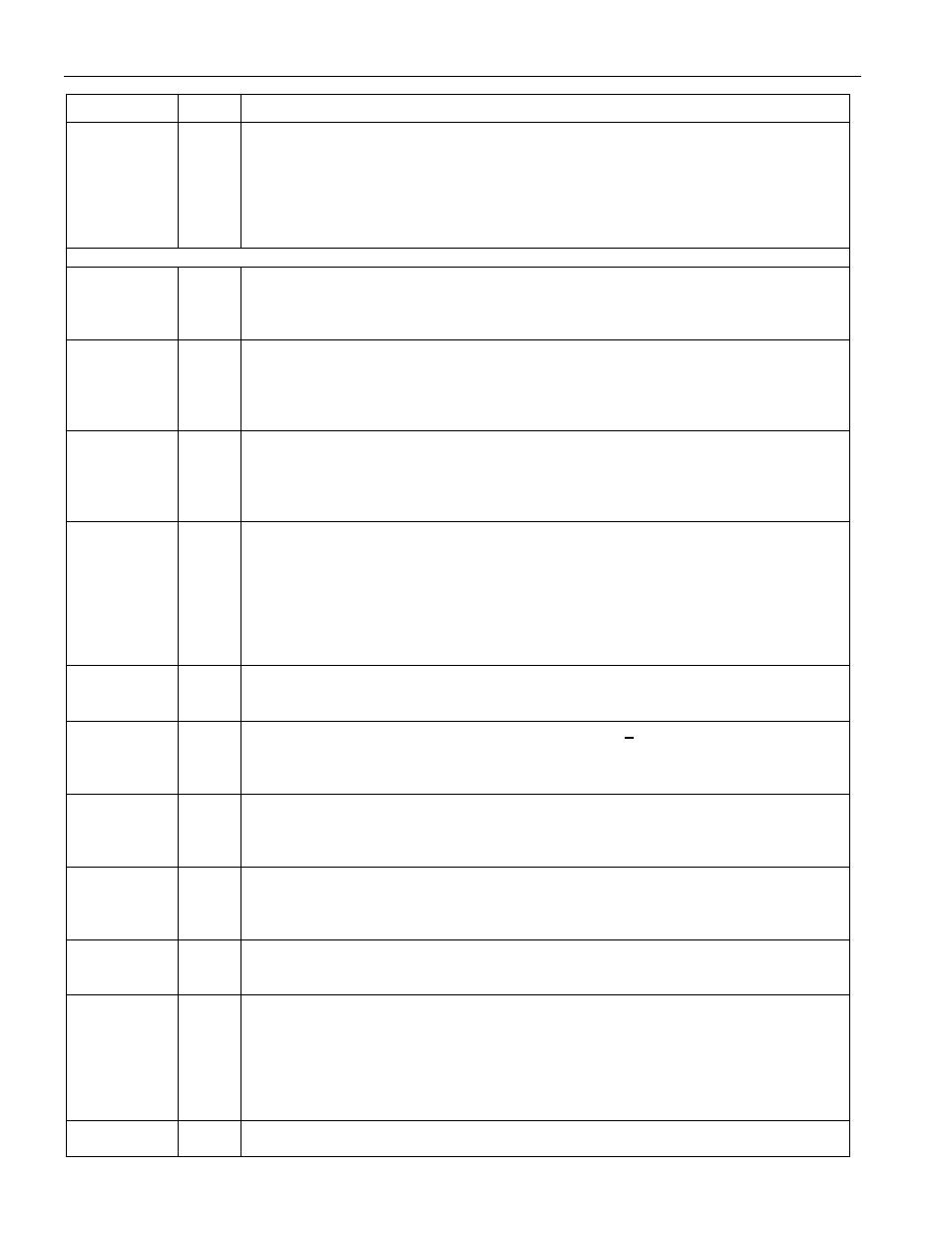

PIN NAME

TYPE

PIN DESCRIPTION

positions of the data on the RSER pin. The signal goes high during each DS3/E3

payload bit and goes low during each DS3/E3 overhead bit. The signal is updated on

the positive clock edge of the referenced clock pin if the clock pin signal is not

inverted, otherwise it is updated on the falling edge of the clock. The signal is typically

referenced to the RCLKO receive clock output pin, but it can be referenced to the

RLCLK clock input pin.

This signal can be inverted.

Microprocessor Interface

D[15:8]

IO

Upper 8 Bits of the Bi-directional 16 or 8 bit data bus

D[15:8]: Upper bits of the 16-bit or 8-bit data bus used to input data during register

writes, and data outputs during register reads. The upper 8 bits are not used in 8 bit

bus mode. Not driven when

CS=1 or RST=0.

D[7]/

SPI_CPOL

IO

Bit 7 of Bi-directional data bus / SPI Bus Clock Polarity

D[7]: Bit 7 of the 16-bit or 8-bit data bus used to input data during register writes, and

data outputs during register reads. Not driven when

CS=1 or RST=0.

SPI_CPOL: This signal selects the clock polarity when SPI = 1. See Section

7.3.4.1

for detailed timing and functionality information. Default setting is low.

D[6]/

SPI_CPHA

IO

Bit 6 of Bi-directional data bus / SPI Bus Clock Phase

D[6]: Bit 6 of the 16-bit or 8-bit data bus used to input data during register writes, and

data outputs during register reads. Not driven when

CS=1 or RST=0.

SPI_CPHA: This signal selects the clock phase when SPI = 1. See Section

7.3.4.1

for

detailed timing and functionality information. Default setting is low.

D[5]/

SPI_SWAP

IO

Bit 5 of Bi-directional data bus / SPI Bit Order Swap

D[5]: Bit 5 of the 16-bit or 8-bit data bus used to input data during register writes, and

data outputs during register reads. Not driven when

CS=1 or RST=0.

SPI_SWAP: This signal is active when SPI=1. The address and data bit order is

swapped when SPI_SWAP is high. The R/W and B bit positions are never changed in

the control word.

0 = MSB is transmitted and received first.

1 = LSB is transmitted and received first.

D[4:3]

IO

Bits 4,3 of Bi-directional data bus

D[4:3]: Bits 3,4 of the 16-bit or 8-bit data bus used to input data during register writes,

and data outputs during register reads. Not driven when

CS=1 or RST=0.

D[2]/

SPI_SCLK

IO

Bit 2 of Bi-directional data bus / SPI Serial Clock Input < 10 MHz

D[2]: Bit 2 of the 16-bit or 8-bit data bus used to input data during register writes, and

data outputs during register reads. Not driven when

CS=1 or RST=0.

SPI_SCLK: SPI Serial Clock Input when SPI = 1.

D[1]/

SPI_MOSI

IO

Bit 1 of Bi-directional data bus / SPI Serial Bus Master-out Slave-in

D[1]: Bit 1 of the 16-bit or 8-bit data bus used to input data during register writes, and

data outputs during register reads. Not driven when

CS=1 or RST=0.

SPI_MOSI: SPI Serial Data Input (Master-out Slave-in) when SPI = 1.

D[0]/

SPI_MISO

IO

Bit 0 of Bi-directional data bus / SPI Serial Bus Master-in Slave-out

D[0]: Bit 0 of the 16-bit or 8-bit data bus used to input data during register writes, and

data outputs during register reads. Not driven when

CS=1 or RST=0.

SPI_MISO: SPI Serial Data Output (Master-in Slave-Out) when SPI = 1.

A[8:1]

I

Address bus (minus LSB) / Device Address [8:1]

A[8:1]: identifies the specific 16 bit registers, or group of 8 bit registers, being

accessed.

A[0] /

BSWAP

Address bus LSB / Byte Swap / Device Address [0]

A[0]: This signal is connected to the lower address bit in 8 bit systems. (WIDTH=0)

1 = Output register bits 15:8 on D[7:0], D[15:8] not driven

0 = Output register bits 7:0 on D[7:0], D[15:8] not driven

BSWAP: This signal is tied high or low in 16 bit systems. (WIDTH=1)

1 = Output register bits 15:8 on D[7:0], 7:0 on D[15:8]

0 = Output register bits 7:0 on D[7:0], 15:8 on D[15:8]

ALE

I

Address Latch Enable

ALE: This signal is used to latch the address on the A[10:0] pins in multiplexed