T3.rsr2 – Rainbow Electronics DS3170 User Manual

Page 178

DS3170 DS3/E3 Single-Chip Transceiver

178 of 233

Bit 10: Application Identification Channel (AIC) – This bit indicates the current state of the Application

Identification Channel (AIC) from the C

11

bit. A one indicates C-bit format and a zero indicates M23 format.

Bit 9: DS3 Idle Signal (IDLE) – When 0, the receive frame processor is not in a DS3 idle signal (Idle) condition.

When 1, the receive frame processor is in an Idle condition.

Bit 8: Receive Unframed All 1’s (RUA1) – When 0, the receive frame processor is not in a receive unframed all

1’s (RUA1) condition. When 1, the receive frame processor is in an RUA1 condition.

Bit 7: Out Of MultiFrame (OOMF) – When 0, the receive frame processor is not in an out of multiframe (OOMF)

condition. When 1, the receive frame processor is in an OOMF condition.

Bit 6: Severely Errored Frame (SEF) – When 0, the receive frame processor is not in a severely errored frame

(SEF) condition. When 1, the receive frame processor is in an SEF condition.

Bit 4: Loss Of Frame (LOF) – When 0, the receive framer is not in a loss of frame (LOF) condition. When 1, the

receive frame processor is in an LOF condition.

Bit 3: Remote Defect Indication (RDI) – This bit indicates the current state of the remote defect indication (RDI)

Bit 2: Alarm Indication Signal (AIS) – When 0, the receive frame processor is not in an alarm indication signal

(AIS) condition. When 1, the receive frame processor is in an AIS condition.

Bit 1: Out Of Frame (OOF) – When 0, the receive framer is not in an out of frame (OOF) condition. When 1, the

receive frame processor is in an OOF condition.

Bit 0: Loss Of Signal (LOS) – When 0, the receive framer is not in a loss of signal (LOS) condition. When 1, the

receive framer is in an LOS condition.

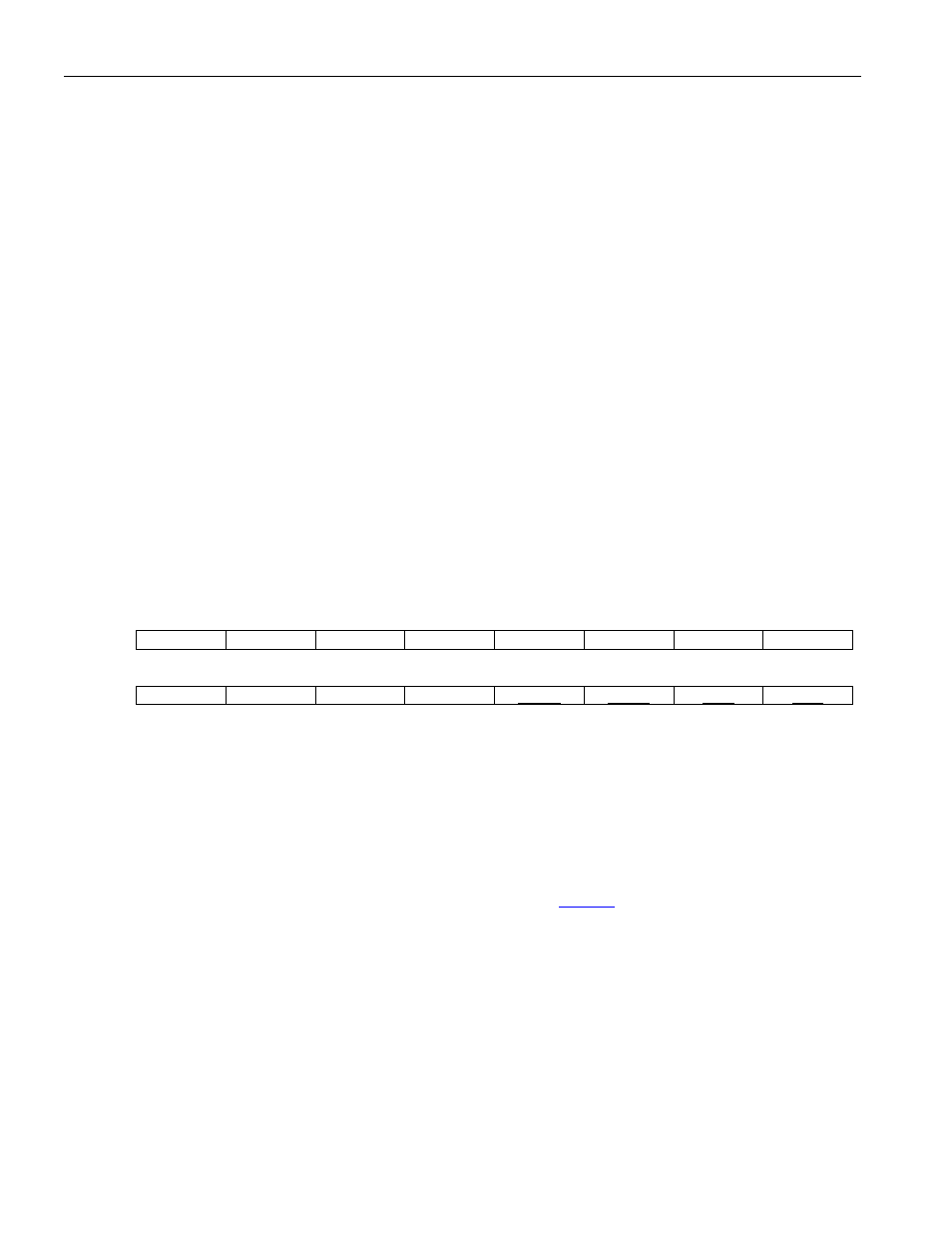

Register Name:

T3.RSR2

Register Description:

T3 Receive Status Register #2

Register Address:

126h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- --

CPEC FBEC PEC FEC

Bit 3: C-bit Parity Error Count (CPEC) – When 0, the C-bit parity error count is zero. When 1, the C-bit parity

error count is one or more. This bit is set to zero in M23 DS3 mode.

Bit 2: Remote Error Indication Count (FBEC) – When 0, the remote error indication count is zero. When 1, the

remote error indication count is one or more. This bit is set to zero in M23 DS3 mode.

Bit 1: P-bit Parity Error Count (PEC) – When 0, the P-bit parity error count is zero. When 1, the P-bit parity error

count is one or more.

Bit 0: Framing Error Count (FEC) – When 0, the framing error count is zero. When 1, the framing error count is

one or more. The type of framing error event counted is determined by

.FECC[1:0]