Receive g.751 e3 register map, Register bit descriptions, Table 11-25. receive g.751 e3 framer register map – Rainbow Electronics DS3170 User Manual

Page 186: E3g751.rcr

DS3170 DS3/E3 Single-Chip Transceiver

186 of 233

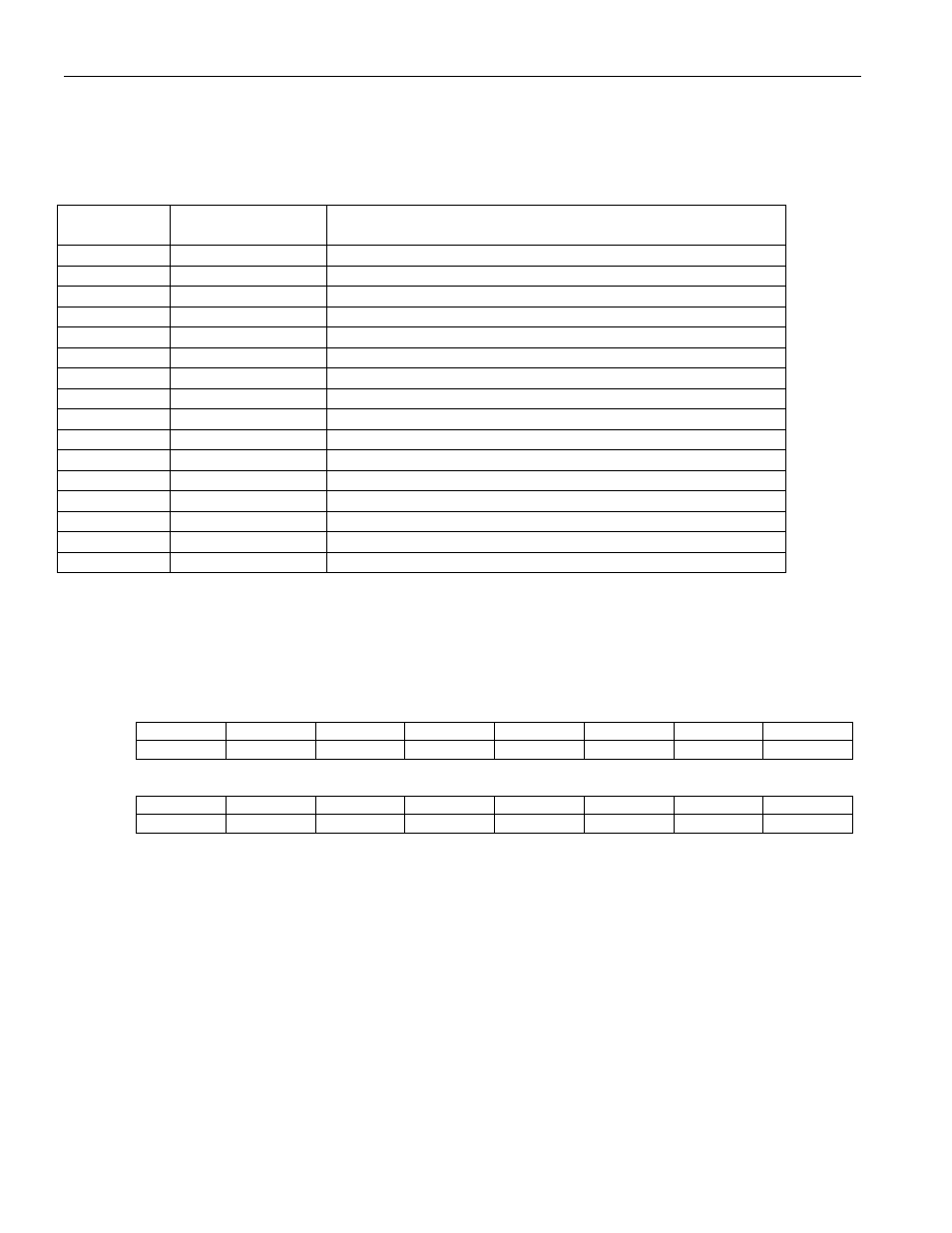

11.9.4 Receive G.751 E3 Register Map

The receive G.751 E3 utilizes eight registers.

Table 11-25. Receive G.751 E3 Framer Register Map

Address

Register

Register Description

120h E3G751.RCR

E3 G.751 Receive Control Register

122h

-- Reserved

124h

E3G751.RSR1

E3 G.751 Receive Status Register #1

126h

E3G751.RSR2

E3 G.751 Receive Status Register #2

128h

E3G751.RSRL1

E3 G.751 Receive Status Register Latched #1

12Ah

E3G751.RSRL2

E3 G.751 Receive Status Register Latched #2

12Ch

E3G751.RSRIE1

E3 G.751 Receive Status Register Interrupt Enable #1

12Eh

E3G751.RSRIE2

E3 G.751 Receive Status Register Interrupt Enable #2

130h

-- Reserved

132h

-- Reserved

134h

E3G751.RFECR

E3 G.751 Receive Framing Error Count Register

136h

-- Reserved

138h

-- Reserved

13Ah

-- Reserved

13Ch

-- Unused

13Eh

-- Unused

11.9.4.1 Register Bit Descriptions

Register Name:

E3G751.RCR

Register Description:

E3 G.751 Receive Control Register

Register Address:

120h

Bit

# 15 14 13 12 11 10 9 8

Name Reserved

Reserved DLS MDAISI AAISD ECC FECC1

FECC0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name RAILE RAILD RAIOD RAIAD ROMD LIP1 LIP0 FRSYNC

Default

0 0 0 0 0 0 0 0

Bit 13: Receive FEAC Data Link Source (DLS) – When 0, the receive FEAC controller will be sourced from the N

bit. When 1, the receive FEAC controller will be sourced from the A bit.

Bit 12: Manual Downstream AIS Insertion (MDAISI) – When 0, manual downstream AIS insertion is disabled.

When 1, manual downstream AIS insertion is enabled.

Bit 11: Automatic Downstream AIS Disable (AAISD) – When 0, the presence of an LOS, OOF, or AIS condition

will cause downstream AIS to be inserted. When 1, the presence of an LOS, OOF, or AIS condition will not cause

downstream AIS to be inserted.

Bit 10: Error Count Control (ECC) – When 0, framing errors will not be counted if an OOF or AIS condition is

present. When 1, framing errors will be counted regardless of the presence of an OOF or AIS condition.