Port.cr2, Port.cr2) – Rainbow Electronics DS3170 User Manual

Page 135

DS3170 DS3/E3 Single-Chip Transceiver

135 of 233

1 = Transmit BERT logic enabled

Bit 7: Transmit Manual Error Insert (TMEI) This bit is used to insert errors in all error insertion logic configured to

use this bit when PORT.CR1.MEIM=0. The error(s) will be inserted when this bit is toggled low to high.

Bit 6 : Transmit Manual Error Insert Mode (MEIM). These bits select the method transmit manual error insertion

for this port for error generators configured to use the external TMEI signal. The global updates are controlled by

the

.MEIMS bit.

0 = Port software update via PORT.CR1.TMEI

1 = Global update source

Bit 4: Performance Monitor Update Mode (PMUM). These bits select the method of updating the performance

monitor registers. The global updates are controlled by the GL.CR1.GPMU bits.

0 = Port software update

1 = Global update

Bit 3: Performance Monitor Register Update (PMU) This bit is used to update all of the performance monitor

registers configured to use this bit when PORT.CR1.PMUM=0. The performance registers configured to use this

signal will be updated with the latest count value and the counters reset when this bit is toggled low to high. The bit

should remain high until the performance register update status bit (PORT.SR.PMS) goes high, then it should be

brought back low which clears the PMS status bit.

Bit 2: Power-Down (PD). When this bit is set, the LIU and digital logic for this port are powered down and

considered “out of service”. The logic is powered down by stopping the clocks. See the

section

0 = Normal operation

1 = Power-down port circuits (default state)

Bit 1: Reset Data Path (RSTDP). When this bit is set, it will force all of the internal data path registers to their

default state. This bit must be set high for a minimum of 100ns and then set back low. See the

section

. Note: The Default State of this bit is 1 (after a general reset (port or global), this bit will be set to

one).

0 = Normal operation

1 = Force all data path registers to their default values

Bit 0: Reset (RST). When this bit is set, it will force all the internal data path and status and control registers

(except this RST bit) of this port to their default state. See the

section

. This bit must be

set high for a minimum of 100ns and then set back low. This software bit is logically OR’ed with the inverted

hardware signal

RST and the

.RST bit.

0 = Normal operation

1 = Force all internal registers to their default values

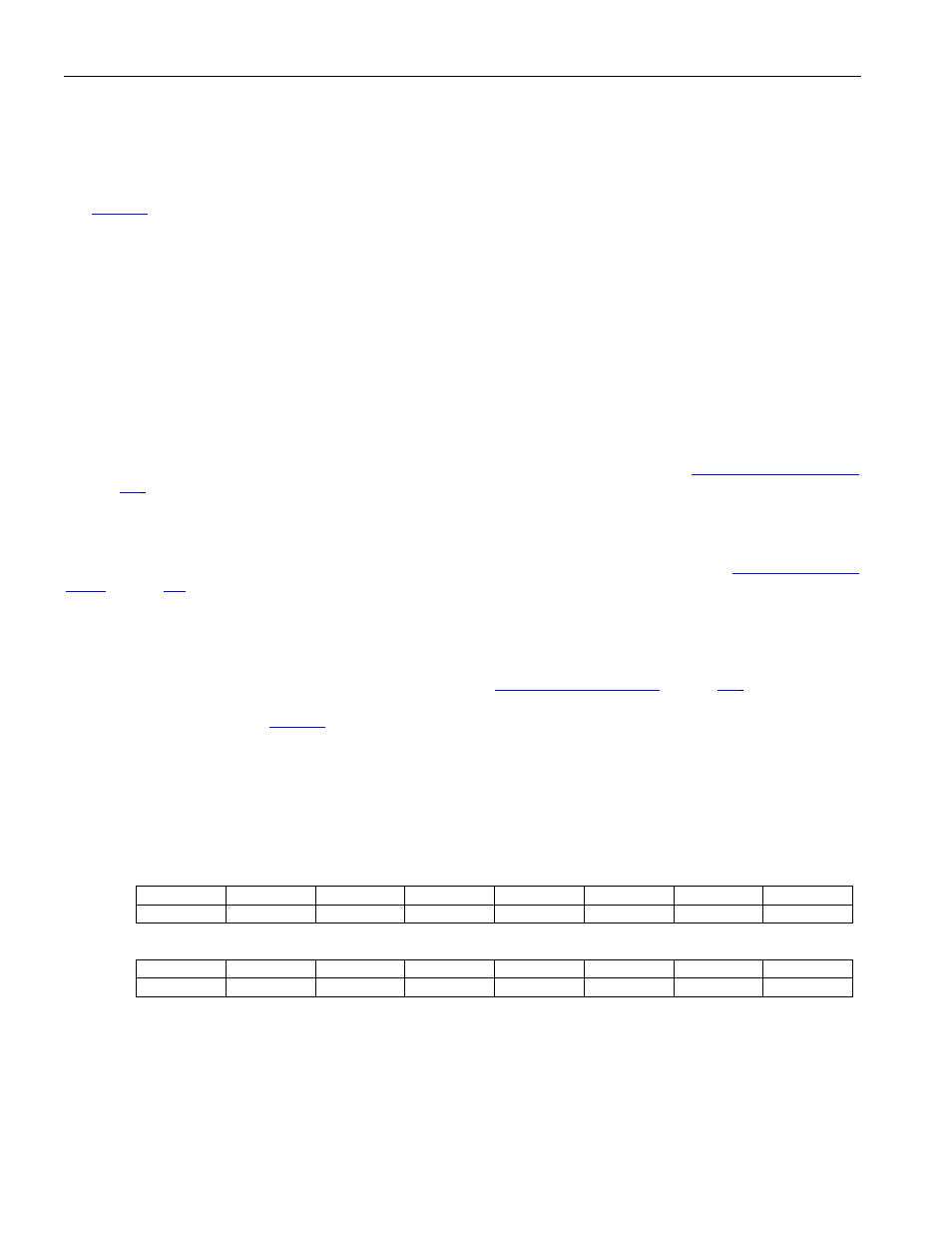

Register Name:

PORT.CR2

Register Description:

Port Control Register 2

Register Address:

042h

Bit

# 15 14 13 12 11 10 9 8

Name TLEN TTS RMON TLBO

RESERVED

LM2 LM1 LM0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

RESERVED

RESERVED

FM2 FM1 FM0

RESERVED RESERVED

RESERVED

Default

0 0 0 0 0 0 0 0

Bit 15: Transmit Line IO Signal Enable (TLEN). This bit is used to enable to transmit line interface output pins

TLCLK, TPOS/TDAT and TNEG.

0 = Disable, force outputs low

1 = Enable normal operation

Bit 14: Transmit LIU Tri-State (TTS) This bit is used to tri-state the transmit TXP and TXN pins. The LIU is still

powered up when the pins are tri-stated. It has no effect when the LIU is disabled and powered down.