Microprocessor interface functional timing, Spi functional timing diagrams, Spi transmission format and cpha polarity – Rainbow Electronics DS3170 User Manual

Page 43: Pin signa, Figure 7-16, Figure 7-18, 4 microprocessor interface functional timing

DS3170 DS3/E3 Single-Chip Transceiver

43 of 233

Figure 7-16. DS3 Framed Mode Receive Serial Interface Pin Timing

RCLKO or

RCLKI

DS3 RSER

DS3 RDEN

RSOFO

DS3 RGCLK

X1

6

7

8

9

10 11 12 13

1

2

3

4

5

14 15

Figure 7-17. E3 G.751 Framed Mode Receive Serial Interface Pin Timing

E3 RSER

E3 RDEN

A

E3 RGCLK

N

FAS 1111010000

RCLKO or

RCLKI

RSOFO

6

7

8

9

10 11 12 13

1

2

3

4

5

14 15

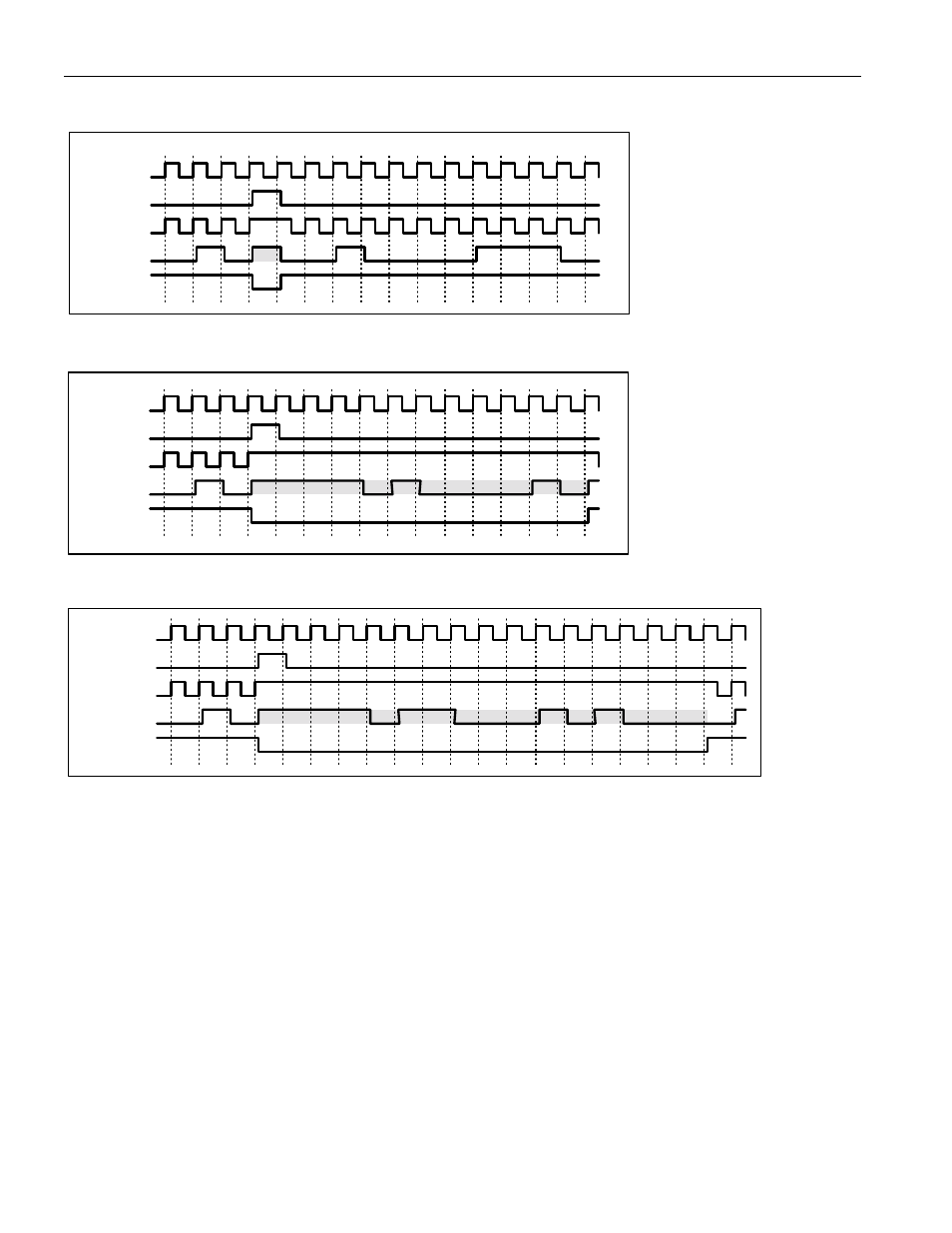

Figure 7-18. E3 G.832 Framed Mode Receive Serial Interface Pin Timing

E3 RSER

E3 RDEN

E3 RGCLK

FA1 11110110

RCLKO or

RCLKI

RSOF

FA2 00101000

6

7

8

9

10 11 12 13

1

2

3

4

5

14 15 16 17 18 19 20

7.3.4 Microprocessor Interface Functional Timing

7.3.4.1 SPI Functional Timing Diagrams

NOTE: The transmit and receive order of the address and data bits are selected by the D[5]/SPI_SWAP pin. The

R/W (read/write) MSB bit and B (burst) LSB bit position is not effected by the D[5]/SPI_SWAP pin setting.

7.3.4.1.1 SPI Transmission Format and CPHA Polarity

When CPHA = 0,

CS may be de-asserted between accesses. An access is defined as one or two control bytes

followed by a data byte.

CS cannot be de-asserted between the control bytes, or between the last control byte and

the data byte. When CPHA = 0,

CS may also remain asserted between accesses. If it remains asserted and the

BURST bit is set, no additional control bytes are expected after the first control byte(s) and data are transferred. If

the BURST bit is set, the address will be incremented for each additional byte of data transferred until

CS is de-

asserted. If

CS remains asserted and the BURST bit is not set, a control byte(s) is expected following the data byte,

and the address for the next access will be received from that. Anytime

CS is de-asserted, the BURST access is

terminated.

When CPHA = 1,

CS may remain asserted for more than one access without being toggled high and then low

again between accesses. If the BURST bit is set, the address should increment and no additional control bytes are