Rainbow Electronics DS2172 User Manual

Ds2172 bit error rate tester (bert)

E

Copyright 1997 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

DS2172

Bit Error Rate Tester (BERT)

DS2172

031197 1/20

FEATURES

•

Generates/Detects digital bit patterns for analyzing,

evaluating and troubleshooting digital communica-

tions systems

•

Operates at speeds from DC to 52 MHz

•

Programmable polynomial length and feedback taps

for generation of any other pseudorandom pattern up

to 32 bits in length including: 2

6

–1, 2

9

–1, 2

11

–1,

2

15

–1, 2

20

–1, 2

23

–1, and 2

32

–1

•

Programmable user–defined pattern and length for

generation of any repetitive pattern up to 32 bits in

length

•

Large 32–bit error count and bit count registers

•

Software programmable bit error insertion

•

Fully independent transmit and receive sections

•

8–bit parallel control port

•

Detects test patterns with bit error rates up to 10

–2

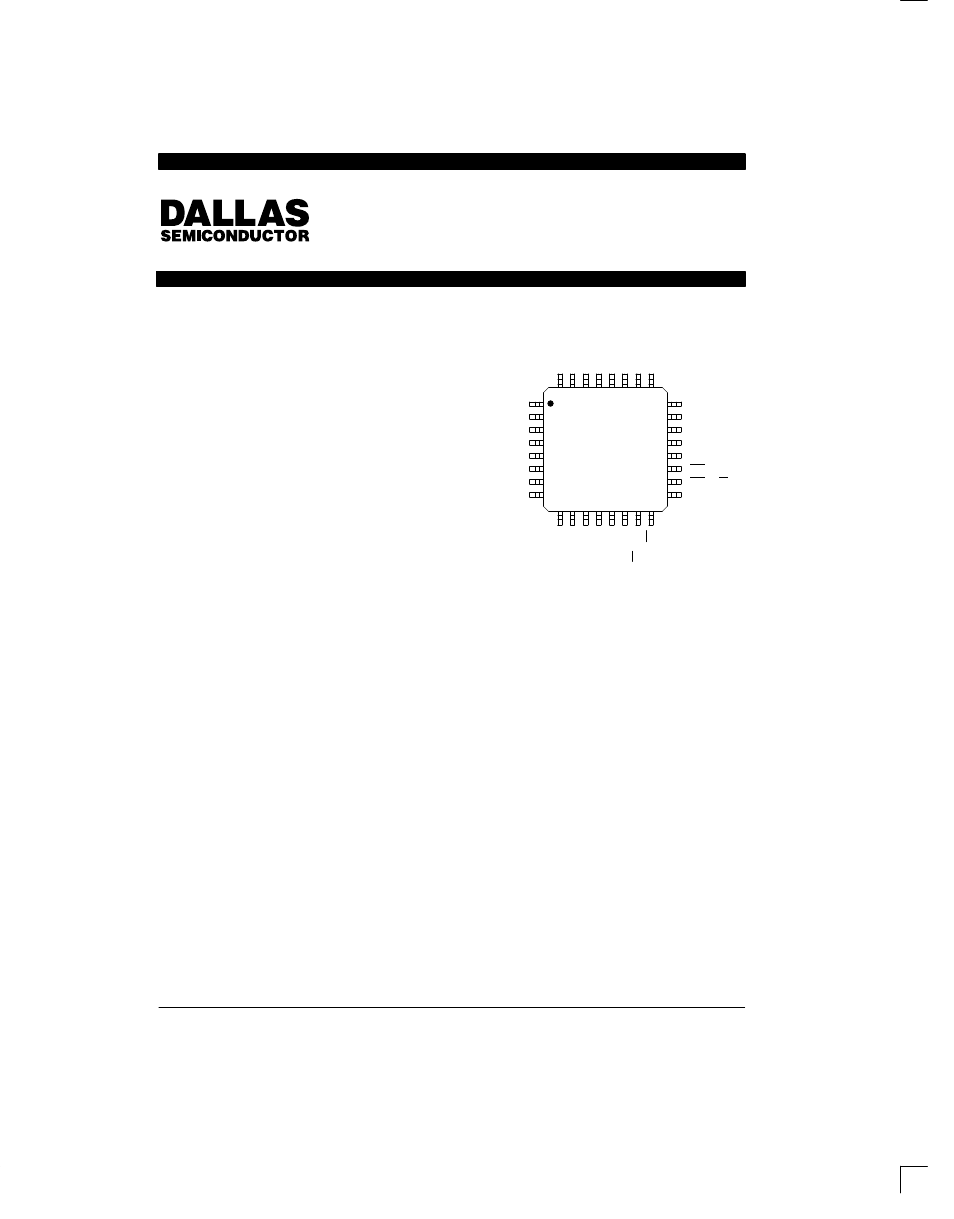

PIN ASSIGNMENT

WR (R/W)

INT

VSS

LC

RL

RLOS

VDD

ALE (AS)

TL

AD0

AD1

TEST

VSS

AD2

AD3

AD4

AD5

AD6

AD7

VSS

VDD

BTS

RD (DS)

CS

TDA

T

A

TDIS

TCLK

VSS

VDD

RCLK

RDIS

RDA

T

A

DS2172

32–PIN TQFP

1

2

3

4

5

6

7

8

24

23

22

21

20

19

18

17

9 10 11 12 13 14 15 16

32 31 30 29 28 27 26 25

DESCRIPTION

The DS2172 Bit Error Rate Tester (BERT) is a software

programmable test pattern generator, receiver, and

analyzer capable of meeting the most stringent error

performance requirements of digital transmission facili-

ties. Two categories of test pattern generation (Pseudo-

random and Repetitive) conform to CCITT/ITU O.151,

O.152, O.153, and O.161 standards. The DS2172

operates at clock rates ranging from DC to 52 MHz. This

wide range of operating frequency allows the DS2172 to

be used in existing and future test equipment, transmis-

sion facilities, switching equipment, multiplexers,

DACs, Routers, Bridges, CSUs, DSUs, and CPE equip-

ment.

The DS2172 user programmable pattern registers pro-

vide the unique ability to generate loopback patterns

required for T1, Fractional–T1, Smart Jack, and other

test procedures. Hence the DS2172 can initiate the

loopback, run the test, check for errors, and finally deac-

tivate the loopback.

The DS2172 consists of four functional blocks: the pat-

tern generator, pattern detector, error counter, and con-

trol interface. The DS2172 can be programmed to gen-

erate any pseudorandom pattern with length up to 2

32–1

bits (See Table 5, Note 9) or any user programmable bit

pattern from 1 to 32 bits in length. Logic inputs can be

used to configure the DS2172 for applications requiring

gap clocking such as Fractional–T1, Switched–56,

DDS, normal framing requirements, and per–channel

test procedures. In addition, the DS2172 can insert

single or 10

–1

to 10

–7

bit errors to verify equipment

operation and connectivity.