E3g832.rmacr – Rainbow Electronics DS3170 User Manual

Page 195

DS3170 DS3/E3 Single-Chip Transceiver

195 of 233

Bits 9 to 8: Framing Error Count Control (FECC[1:0]) – These two bits control the type of framing error events

that are counted.

00 = count OOF occurrences (counted regardless of the setting of the ECC bit)..

01 = count each bit error in FA1 and FA2 (up to 16 per frame).

10 = count frame alignment word (FA1 and FA2) errors (up to one per frame).

11 = count FA1 byte errors and FA2 byte errors (up to 2 per frame).

Bit 7: Receive Alarm Indication on LOF Enable (RAILE) – When 0, an LOF condition does not affect the receive

alarm indication signal (RAI). When 1, an LOF condition will cause the transmit E3 RDI bit to be set to one if

transmit automatic RDI is enabled.

Bit 6: Receive Alarm Indication on LOS Disable (RAILD) – When 0, an LOS condition will cause the transmit E3

RDI bit to be set to one if transmit automatic RDI is enabled. When 1, an LOS condition does not affect the RAI

signal.

Bit 5: Receive Alarm Indication on OOF Disable (RAIOD) – When 0, an OOF condition will cause the transmit

E3 RDI bit to be set to one if transmit automatic RDI is enabled. When 1, an OOF condition does not affect the RAI

signal.

Bit 4: Receive Alarm Indication on AIS Disable (RAIAD) – When 0, an AIS condition will cause the transmit E3

RDI bit to be set to one if transmit automatic RDI is enabled. When 1, an AIS condition does not affect the RAI

signal.

Bit 3: Receive Overhead Masking Disable (ROMD) – When 0, the E3 overhead positions in the outgoing E3

payload will be marked as overhead by RDEN. When 1, the E3 overhead positions in the outgoing E3 payload will

be marked as data by RDEN.

Bits 2 to 1: LOF Integration Period (LIP[1:0]) – These two bits determine the OOF integration period for

declaring LOF.

00 = OOF is integrated for 3 ms before declaring LOF.

01 = OOF is integrated for 2 ms before declaring LOF.

10 = OOF is integrated for 1 ms before declaring LOF.

11 = LOF is declared at the same time as OOF.

Bit 0: Force Framer Resynchronization (FRSYNC) – A 0 to 1 transition forces. an OOF condition at the next

framing word check. This bit must be cleared and set to one again to force another resynchronization. Note: The

OOF condition is created by failing the most recent four data path frame alignment word checks.

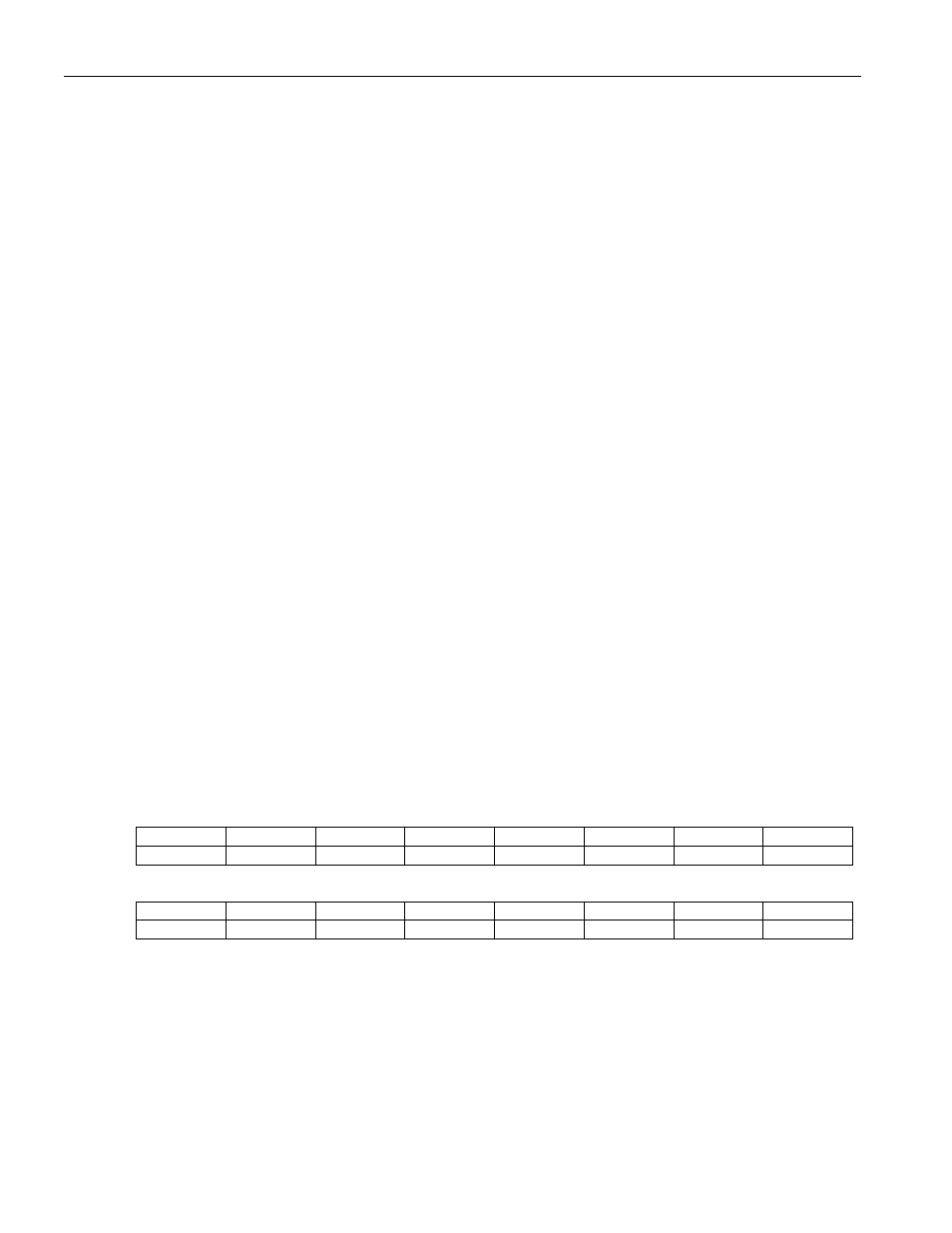

Register Name:

E3G832.RMACR

Register Description:

E3 G.832 Receive MA Byte Control Register

Register Address:

122h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- --

EPT2

EPT1

EPT0

TIED

Default

0 0 0 0 0 0 0 0

Bits 3 to 1: Expected Payload Type (EPT[2:0]) – These three bits contain the expected value of the payload

type.

Bit 0: Timing Source Indicator Bit Extraction Disable (TIED) – When 0, the four timing source indications bits

are extracted from the last three bits of the MA byte (MA[6:8]), and stored in a register. When 1, timing source

indicator bit extraction is disabled, and the last three bits of the MA byte are integrated and stored in a register.