T3.teir – Rainbow Electronics DS3170 User Manual

Page 175

DS3170 DS3/E3 Single-Chip Transceiver

175 of 233

Bit 1: Transmit Frame Generation Disabled (TFGD) –

0 = Transmit Frame Generation is enabled

1 = Transmit Frame Generation is disabled; DS3 overhead positions in the incoming DS3 payload

will be passed through to error insertion. Note: Frame generation will still overwrite the P-bits if

PBGE = 1. Also, the DS3 overhead periods can still be overwritten by error insertion, overhead

insertion, or AIS/Idle generation.

Bit 0: Transmit Alarm Indication Signal (TAIS) –

0 = Transmit Alarm Indication Signal is not inserted

1 = Transmit Alarm Indication Signal is inserted into data stream payload

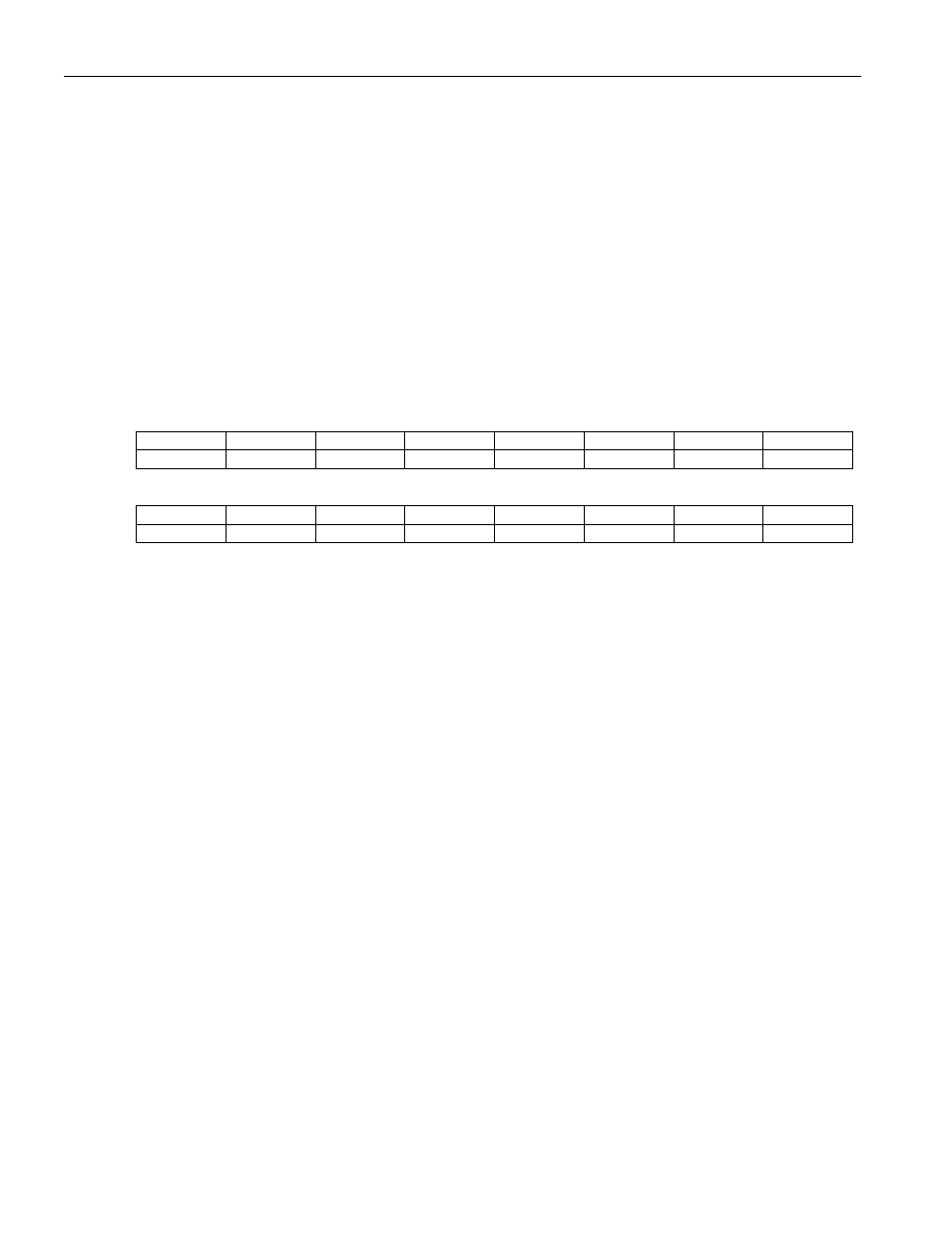

Register Name:

T3.TEIR

Register Description:

T3 Transmit Error Insertion Register

Register Address:

11Ah

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- --

CCPEIE

CPEI

CFBEIE

FBEI

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name Reserved CPEIE PEI FEIC1 FEIC0 FEI

TSEI MEIMS

Default

0 0 0 0 0 0 0 0

Bit 11: Continuous C-bit Parity Error Insertion Enable (CCPEIE) – When 0, single C-bit parity error insertion is

enabled. When 1, continuous C-bit parity error insertion is enabled, and C-bit parity errors will be transmitted

continuously if CPEI is high.

Bit 10: C-bit Parity Error Insertion Enable (CPEI) – When 0, C-bit parity error insertion is disabled. When 1, C-bit

parity error insertion is enabled.

Bit 9: Continuous Far-End Block Error Insertion Enable (CFBEIE) – When 0, single far-end block error

insertion is enabled. When 1, continuous far-end block error insertion is enabled, and far-end block errors will be

transmitted continuously if FBEI is high.

Bit 8: Far-End Block Error Insertion Enable (FBEI) – When 0, far-end block error insertion is disabled. When 1,

far-end block error insertion is enabled.

Bit 6: Continuous P-bit Parity Error Insertion Enable (CPEIE) – When 0, single P-bit parity error insertion is

enabled. When 1, continuous P-bit parity error insertion is enabled, and P-bit parity errors will be transmitted

continuously if PEI is high.

Bit 5: P-bit Parity Error Insertion Enable (PEI) – When 0, P-bit parity error insertion is disabled. When 1, P-bit

parity error insertion is enabled.

Bits 4 to 3: Framing Error Insertion Control (FEIC[1:0]) – These two bits control the framing error event to be

inserted.

00 = F-bit error.

01 = M-bit error.

10 = SEF error.

11 = OOMF error.

Bit 2: Framing Error Insertion Enable (FEI) – When 0, framing error insertion is disabled. When 1, framing error

insertion is enabled.

Bit 1: Transmit Single Error Insert (TSEI) – This bit causes an error of the enabled type(s) to be inserted in the

transmit data stream if manual error insertion is disabled (MEIMS = 0). A 0 to 1 transition causes a single error to

be inserted. For a second error to be inserted, this bit must be set to 0, and back to 1. Note: If MEIMS is low, and

this bit transitions more than once between error insertion opportunities, only one error will be inserted.