Receiver power-down, Receiver jitter tolerance, Figure 9-32. receiver jitter tolerance – Rainbow Electronics DS3170 User Manual

Page 116

DS3170 DS3/E3 Single-Chip Transceiver

116 of 233

The ALOS detector in the AGC/equalizer block detects that the incoming signal is less than or equal to a signal

level approximately 24dB below nominal, and mutes the data coming out of the clock and data recovery block.

(24dB below nominal in the “tolerance range” of G.775, where LOS may or may not be declared.)

For E3 LOS Clear:

The ALOS detector in the AGC/equalizer block detects that the incoming signal is greater than or equal to a signal

level approximately 18dB below nominal, and enables data to come out of the CDR block. (18dB is in the

“tolerance range” of G.775, where LOS may or may not be declared.)

9.12.5.6 Receiver Power-Down

To minimize power consumption when the receiver is not being used, write a one to the PORT.CR1.PD bit. When

the receiver is powered down, the RCLKO pin is tri-stated. In addition, the RXP and RXN pins become high

impedance.

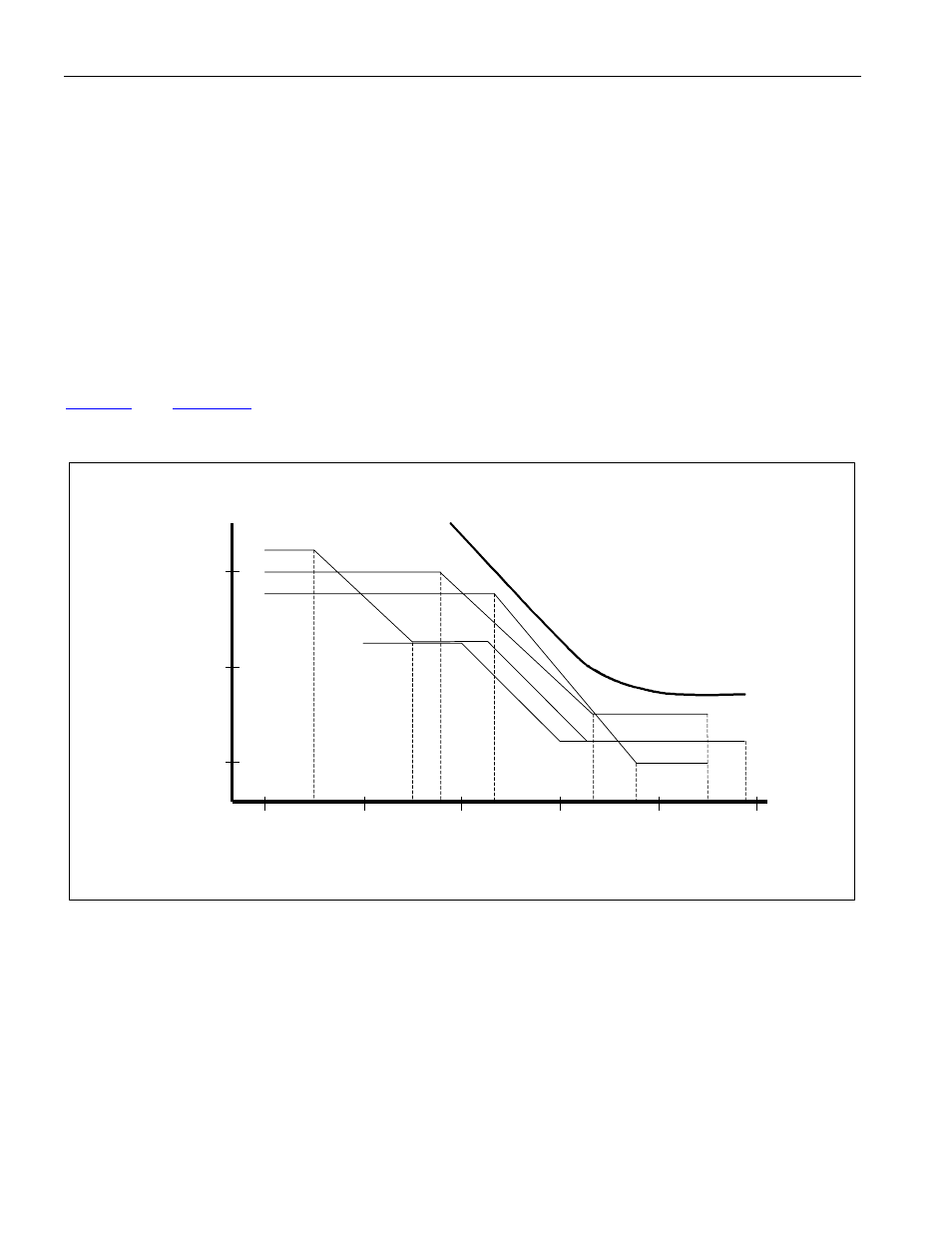

9.12.5.7 Receiver Jitter Tolerance.

The receiver exceeds the input jitter tolerance requirements of all applicable telecommunication standards in

. See

Figure 9-32. Receiver Jitter Tolerance

10

100

1k

10k

100k

1M

60k

22.3k

2.3k

669

0.1

1.0

10

300k

800k

300

30

0.1

0.15

0.3

10

5

1.5

E3 G.823

DS3 GR-499 Cat II

DS3 GR-499 Cat I

DS3170 JITTER TOLERANCE

15

STS-1 GR253

FREQUENCY (Hz)

JI

TTE

R T

O

LE

RA

NCE

(

U

I

P-P

)