Port.srl, Port.srie – Rainbow Electronics DS3170 User Manual

Page 142

DS3170 DS3/E3 Single-Chip Transceiver

142 of 233

Bit 1: Receive Loss Of Lock Status (RLOL) This bits indicates the status of the receive LIU clock recovery PLL

circuit.

0 = Locked to the incoming signal

1 = Not locked to the incoming signal

Bit 0: Performance Monitoring Update Status (PMS) This bits indicates the status of all active performance

monitoring register and counter update signals in this port. It is an “AND” of all update status bits and is not set until

all performance registers are updated and the counters reset. In software update modes, the update request bit

PORT.CR1.PMU should be held high until this status bit goes high.

0 = The associated update request signal is low

1 = The requested performance register updates are all completed

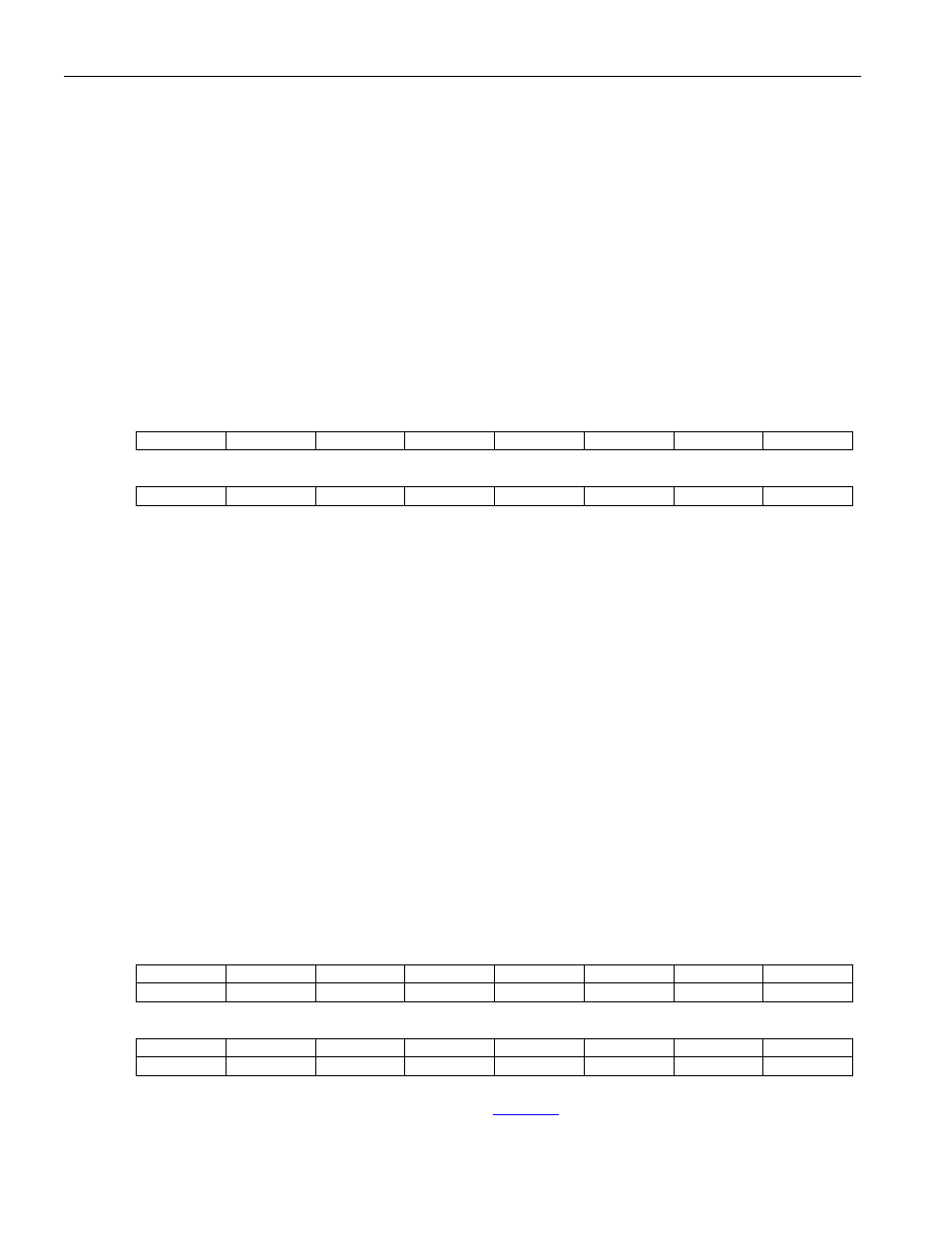

Register Name:

PORT.SRL

Register Description:

Port Status Register Latched

Register Address:

054h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Bit

# 7 6 5 4 3 2 1 0

Name

RLCLKL

TCLKIL

-- -- --

TDML

RLOLL

PMSL

Bit 7: Receive Line Clock Activity Status Latched (RLCLKL) This bit will be set when the signal on the RLCLK

pin or the recovered clock from the LIU for this port is active.

Bit 6: Transmit Input Clock Activity Status Latched (TCLKIL) This bit will be set when the signal on the TCLKI

pin for this port is active.

Bit 2: Transmit Driver Monitor Status Latched (TDML) This bit will be set when the PORT.SR.TDM status bit

changes from low to high. This bit will also set the PORT.ISR.PSR status bit if the PORT.SRIE.TDMIE bit is

enabled. The interrupt pin will be driven when this bit is set, the PORT.SRIE.TDMIE bit is set, and the

corresponding GL.ISRIE.PISRIE bit is also set.

Bit 1: Receive Loss Of Lock Status Latched (RLOLL) This bit will be set when the PORT.SR.RLOL status bit

changes from low to high. This bit will also set the PORT.ISR.PSR status bit if the PORT.SRIE.RLOLIE bit is

enabled. The interrupt pin will be driven when this bit is set, the PORT.SRIE.RLOLIE bit is set, and the

corresponding GL.ISRIE.PISRIE bit is also set.

Bit 0: Performance Monitoring Update Status Latched (PMSL) This bit will be set when the PORT.SR.PMS

status bit changes from low to high. This bit will also set the PORT.ISR.PSR status bit if the PORT.SRIE.PMUIE bit

is enabled. The interrupt pin will be driven when this bit is set, the PORT.SRIE.PMUIE bit is set, and the

PORT.SRIE.PMSIE bit are set.

Register Name:

PORT.SRIE

Register Description:

Port Status Register Interrupt Enable

Register Address:

056h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- -- --

TDMIE

RLOLIE

PMSIE

Default

0 0 0 0 0 0 0 0

Bit 2: Transmit Driver Monitor Latched Status Interrupt Enable (TDMIE) The interrupt pin will be driven when

this bit is enabled and the PORT.SRL.TDML bit is set and the

.PISRIE bit is enabled.