Rainbow Electronics DS2141A User Manual

Features, Description, Pin assignment

E

Copyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

DS2141A

T1 Controller

DS2141A

021997 1/35

FEATURES

•

DS1/ISDN–PRI framing transceiver

•

Frames to D4, ESF, and SLC–96 formats

•

Parallel control port

•

Onboard, dual two–frame elastic store slip buffers

•

Extracts and inserts robbed–bit signaling

•

Programmable output clocks

•

Onboard FDL support circuitry

•

5V supply; low–power CMOS

•

Available in 40–pin DIP and 44–pin PLCC (DS2141Q)

•

Compatible with DS2186 Transmit Line Interface,

DS2187 Receive Line Interface, DS2188 Jitter Atten-

uator, DS2290 T1 Isolation Stik, and DS2291 T1 Long

Loop Stik.

DESCRIPTION

The DS2141A is a comprehensive, software–driven T1

framer. It is meant to act as a slave or coprocessor to a

microcontroller or microprocessor. Quick access via

the parallel control port allows a single micro to handle

many T1 lines. The DS2141A is very flexible and can be

configured into numerous orientations via software.

The software orientation of the device allows the user to

modify their design to conform to future T1 specification

changes. The controller contains a set of 62 8–bit inter-

nal registers which the user can access. These internal

registers are used to configure the device and obtain in-

formation from the T1 link. The device fully meets all of

the latest T1 specifications including ANSI

T1.403–1989, AT&T TR 62411 (12–90), and CCITT

G.704 and G.706.

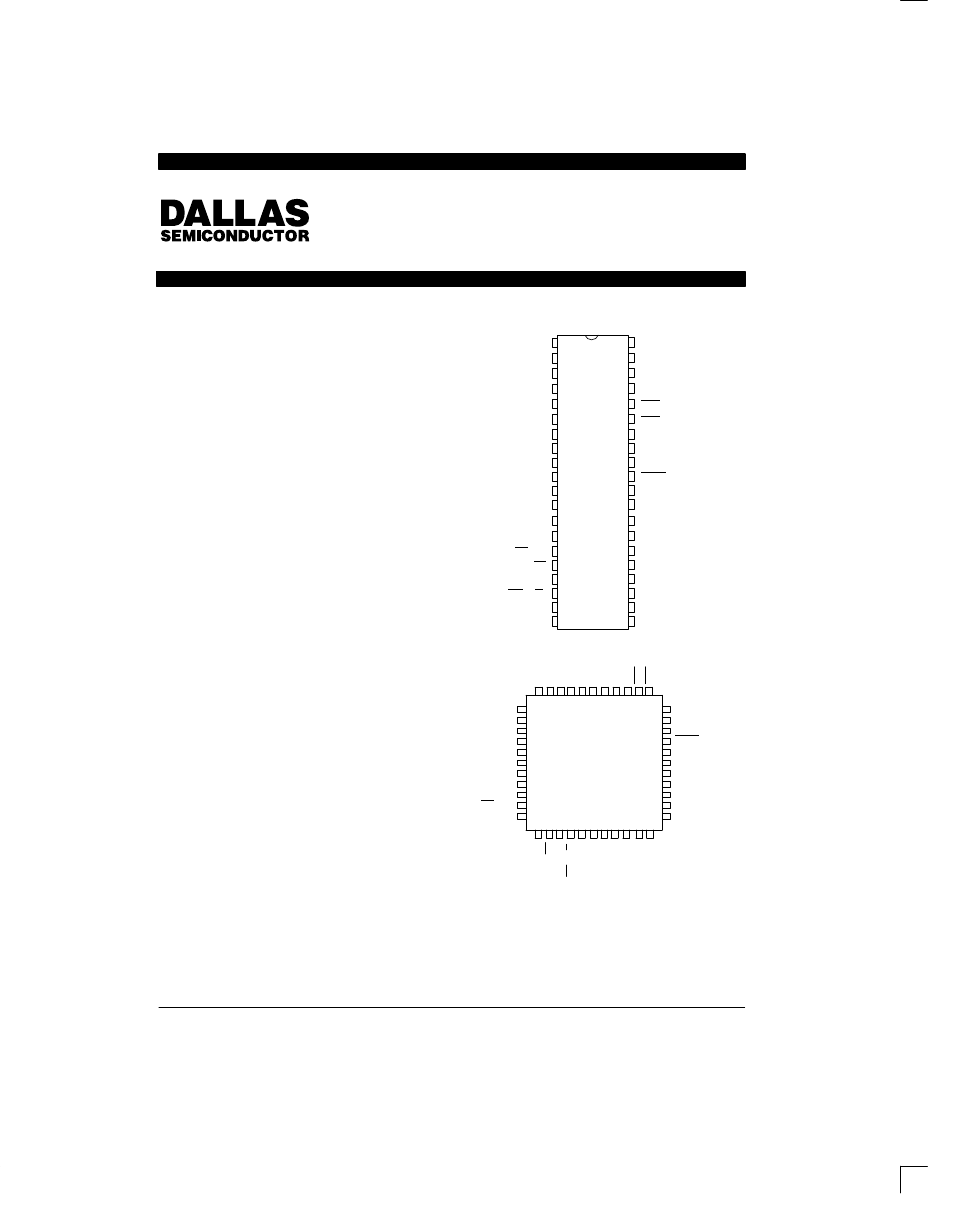

PIN ASSIGNMENT

LI_SDI

LI_CS

RD (DS)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

40–PIN DIP (600 MIL)

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

TCLK

TSER

TCHCLK

TPOS

TNEG

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

BTS

RD(DS)

CS

ALE(AS)

WR(R/W)

RLINK

VSS

VDD

TSYNC

TLINK

TLCLK

INT1

INT2

RLOS/LOTC

TCHBLK

RCHBLK

LI_CS

LI_CLK

SYSCLK

RNEG

RPOS

RSYNC

RSER

RCHCLK

RCLK

RLCLK

LI_SDI

1

2

3

4

5

6

44 43 42 41 40

1819 202122 2324 25 26 27 28

TNEG

TPOS

TCHCLK

TSER

TCLK

VDD

TSYNC

TLINK

TLCLK

INT1

INT2

NC

CS

ALE(AS)

WR(R/W)

RLINK

VSS

RLCLK

RCLK

RCHCLK

RSER

RSYNC

44–PIN PLCC

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

BTS

NC

RLOS/LOTC

TCHBLK

RCHBLK

LI_CLK

NC

NC

SYSCLK

RNEG

RPOS

7

8

9

10

11

12

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29