E3g832.rmabr, E3g832.rngbr – Rainbow Electronics DS3170 User Manual

Page 200

DS3170 DS3/E3 Single-Chip Transceiver

200 of 233

Bit 0: Framing Error Count Interrupt Enable (FECIE) – This bit enables an interrupt if the FECL bit is set and the

bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

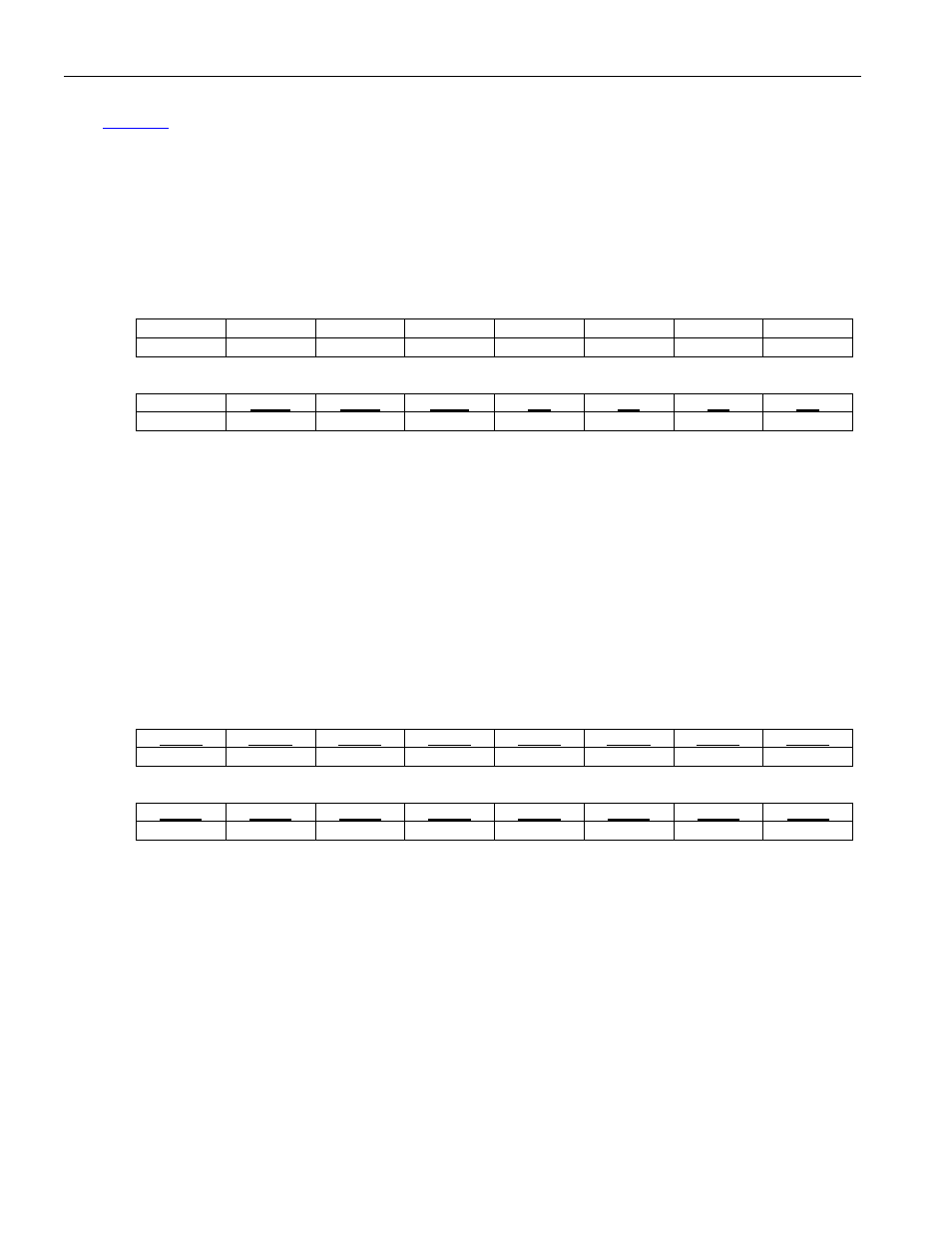

Register Name:

E3G832.RMABR

Register Description:

E3 G.832 Receive MA Byte Register

Register Address:

130h

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name -- RPT2 RPT1 RPT0 TI3 TI2 TI1 TI0

Default

0 0 0 0 0 0 0 0

Bits 6 to 4: Receive Payload Type (RPT[2:0]) – These three bits are the integrated version of the payload type

(MA[3:5]) from the MA byte.

Bits 3 to 0: Receive Timing Source Indication (TI[3:0]) – When timing source indicator extraction is enabled,

these four bits are the integrated version of the four timing source indicator bits extracted from the last three bits of

the MA byte (MA[6:8]). When timing source indicator bit extraction is disabled, TI[3] is zero, and TI[2:0] contain the

integrated version of the last three bits of the MA byte.

Register Name:

E3G832.RNGBR

Register Description:

E3 G.832 Receive NR and GC Byte Register

Register Address:

132h

Bit

# 15 14 13 12 11 10 9 8

Name RGC7 RGC6 RGC5 RGC4 RGC3 RGC2 RGC1 RGC0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name RNR7 RNR6 RNR5 RNR4 RNR3 RNR2 RNR1 RNR0

Default

0 0 0 0 0 0 0 0

Bits 15 to 8: Receive GC Byte (RGC[7:0]) – These eight bits are the integrated version of the GC byte as

extracted from the E3 frame.

Bits 7 to 0: Receive NR Byte (RNR[7:0]) – These eight bits are the integrated version of the NR byte as extracted

from the E3 frame.