Receive ds3 register map, Register bit descriptions, Table 11-23. receive ds3 framer register map – Rainbow Electronics DS3170 User Manual

Page 176: T3.rcr

DS3170 DS3/E3 Single-Chip Transceiver

176 of 233

Bit 0: Manual Error Insert Mode Select (MEIMS) – When 0, error insertion is initiated by the TSEI register bit.

When 1, error insertion is initiated by the transmit manual error insertion signal (TMEI). Note: If TMEI or TSEI is

one, changing the state of this bit may cause an error to be inserted.

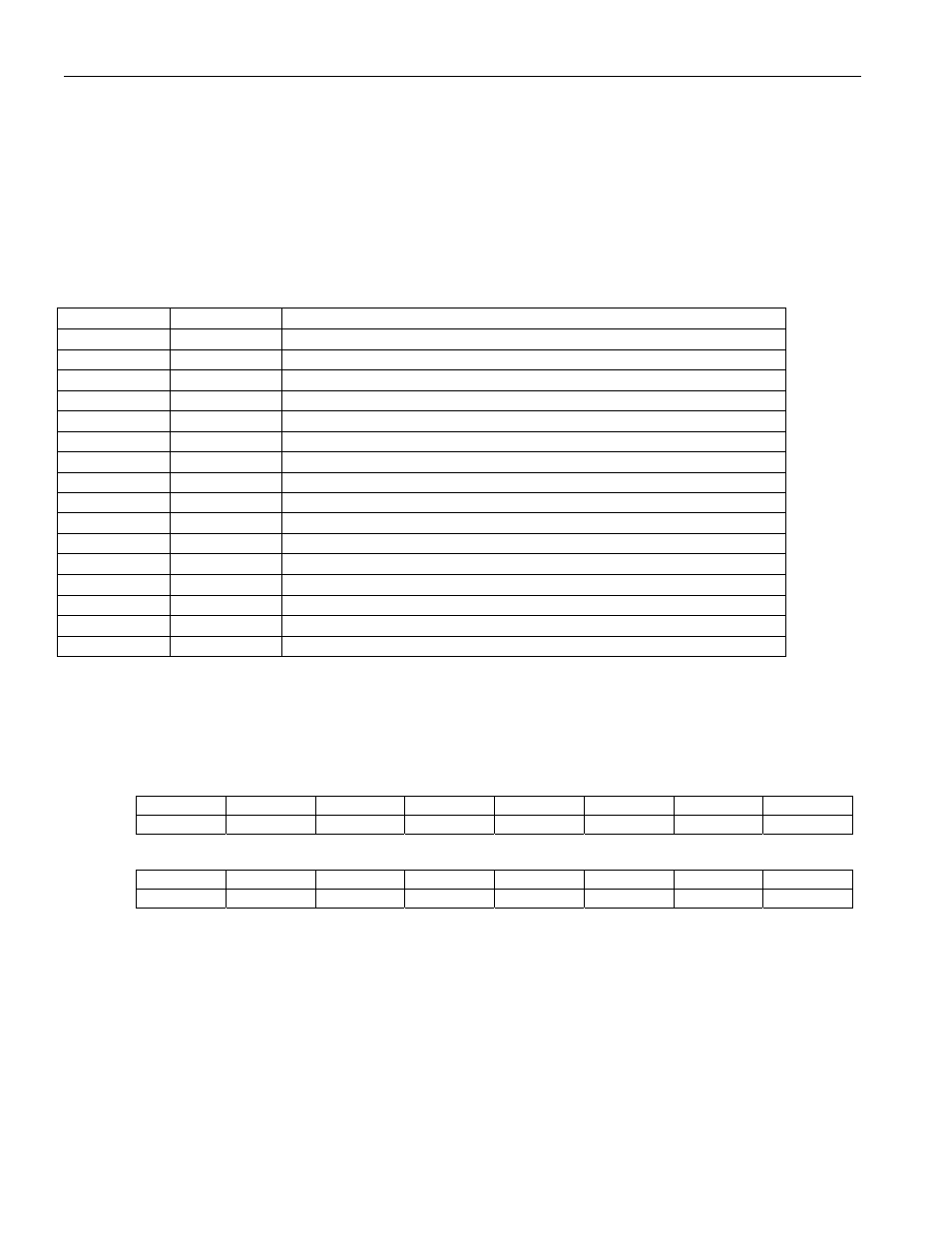

11.9.2 Receive DS3 Register Map

The receive DS3 utilizes eleven registers. Two registers are shared for C-Bit and M23 DS3 modes. The M23 DS3

mode does not use the RFEBER or RCPECR count registers.

Table 11-23. Receive DS3 Framer Register Map

Address Register

Register

Description

120h

T3.RCR

T3 Receive Control Register

122h

-- Reserved

124h

T3.RSR1

T3 Receive Status Register #1

126h

T3.RSR2

T3 Receive Status Register #2

128h

T3.RSRL1

T3 Receive Status Register Latched #1

12Ah

T3.RSRL2

T3 Receive Status Register Latched #2

12Ch

T3.RSRIE1

T3 Receive Status Register Interrupt Enable #1

12Eh

T3.RSRIE2

T3 Receive Status Register Interrupt Enable #2

130h

-- Reserved

132h

-- Reserved

134h

T3.RFECR

T3 Receive Framing Error Count Register

136h

T3.RPECR

T3 Receive P-bit Parity Error Count Register

138h

T3.RFBECR

T3 Receive Far-End Block Error Count Register

13Ah

T3.RCPECR

T3 Receive C-bit Parity Error Count Register

13Ch

-- Unused

13Eh

-- Unused

11.9.2.1 Register Bit Descriptions

Register Name:

T3.RCR

Register Description:

T3 Receive Control Register

Register Address:

120h

Bit

# 15 14 13 12 11 10 9 8

Name Reserved

COVHD MAOD MDAISI AAISD ECC FECC1 FECC0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name RAILE RAILD RAIOD RAIAD ROMD LIP1 LIP0 FRSYNC

Default

0 0 0 0 0 0 0 0

Bit 14: C-bit Overhead Masking Disable (COVHD) – When 0, the C-bit positions will be marked as overhead

(RDEN=0). When 1, the C-bit positions will be marked as data (RDEN=1). This bit is ignored in C-bit DS3 mode or

when the ROMD bit is set to one.

Bit 13: Multiframe Alignment OOF Disable (MAOD) – When 0, an OOF condition is declared whenever an

OOMF or SEF condition is declared. When 1, an OOF condition is declared only when an SEF condition is

declared.

Bit 12: Manual Downstream AIS Insertion (MDAISI) – When 0, manual downstream AIS insertion is disabled.

When 1, manual downstream AIS insertion is enabled.