Liu – line interface unit, General description, Features – Rainbow Electronics DS3170 User Manual

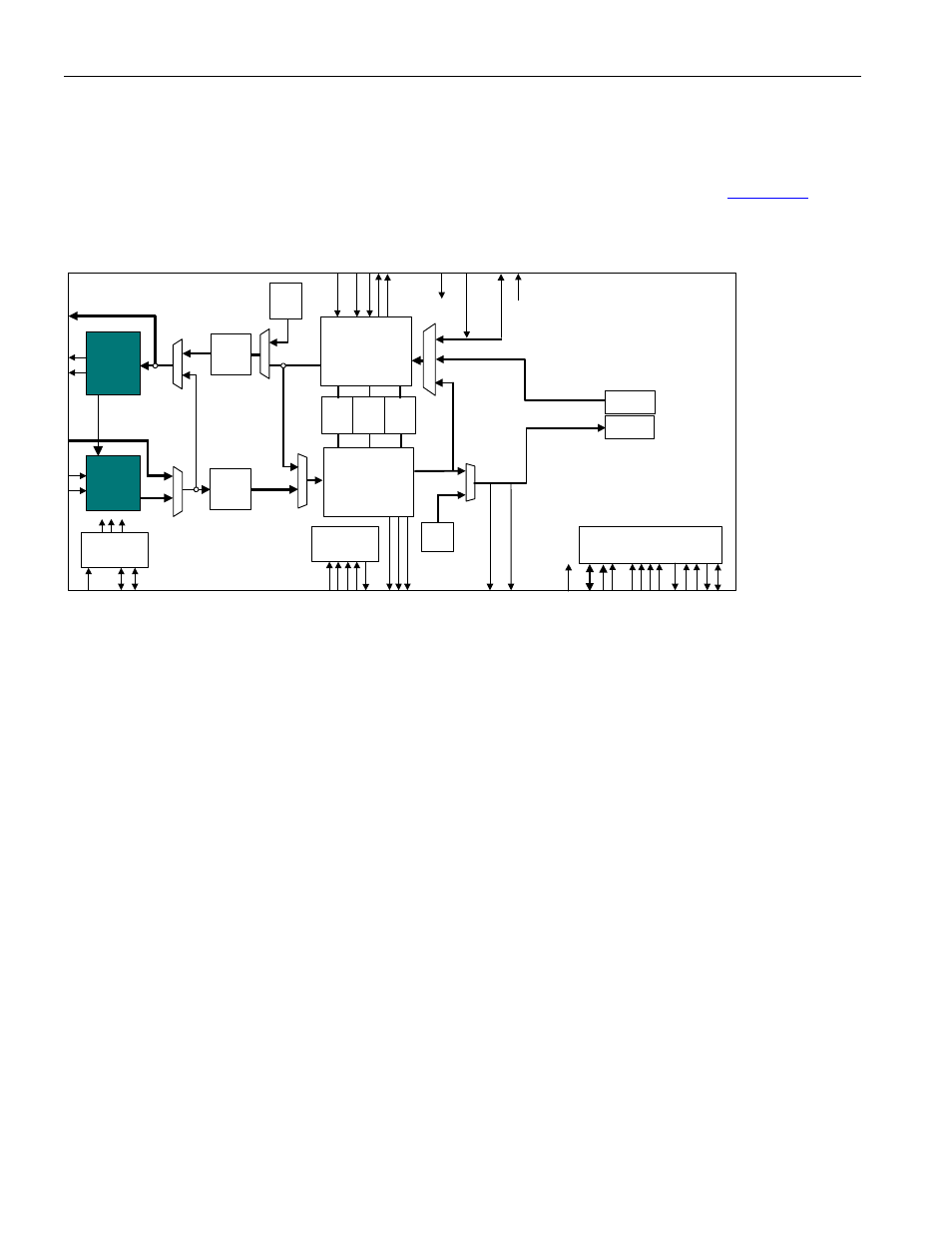

Page 112: Transmitter, Receiver, Detailed description, Liu – l, Nterface, Figure 9-30. liu functional diagram, 12 liu – line interface unit

DS3170 DS3/E3 Single-Chip Transceiver

112 of 233

9.12 LIU – Line Interface Unit

9.12.1 General Description

The line interface units (LIUs) perform the functions necessary for interfacing at the physical layer to DS3 or E3

lines. The LIU has independent receive and transmit paths and a built-in jitter attenuator. See

for the

location within the DS3170 device of the LIU.

Figure 9-30. LIU Functional Diagram

DS3/E3

Transmit

LIU

IEEE P1149.1

JTAG Test

Access Port

Microprocessor

Interface

HDLC

FEAC

LLB

DL

B

DS3 / E3

Transmit

Formatter

DS3 / E3

Receive

Framer

Trail

Trace

Buffer

DS3/E3

Receive

LIU

TAIS

TUA1

Clock Rate

Adapter

TX BERT

RX BERT

PL

B

AL

B

UA1

GEN

B3ZS/

HDB3

Encoder

B3ZS/

HDB3

Decoder

9.12.2 Features

· Performs Receive Clock/Data Recovery and Transmit Waveshaping

· Jitter Attenuators can be Placed in Either the Receive or Transmit Paths

· Interfaces to 75W Coaxial Cable at Lengths Up to 380 meters (DS3), 440 meters (E3)

· Use 1:2 Transformers on Tx and RX

· Requires Minimal External Components

· Local and Remote Loopbacks

9.12.2.1 Transmitter

· Gapped clock capable up to 52MHz

· Wide 50 ±20% transmit clock duty cycle

· Clock inversion for glueless interfacing

· Unframed all-ones generator (E3 AIS)

· Line build-out (LBO) control

· Tri-state line driver outputs support protection switching applications

· Per-channel power-down control

· Output driver monitor

9.12.2.2 Receiver

· AGC/equalizer block handles from 0 to 15dB of cable loss

· Loss-of-lock (LOL) PLL status indication

· Interfaces directly to a DSX monitor signal (~20dB flat loss) using built-in preamp

· Digital and analog loss-of-signal (LOS) detectors (ANSI T1.231 and ITU G.775)

· Clock inversion for glueless interfacing

· Per-channel power-down control

9.12.3 Detailed Description

The receiver performs clock and data recovery from an alternate mark inversion (AMI) coded signal or a B3ZS- or

HDB3-coded AMI signal and monitors for loss of the incoming signal. The transmitter drives standard pulse-shape