Hdlc.rsrie, Hdlc.rfdr – Rainbow Electronics DS3170 User Manual

Page 161

DS3170 DS3/E3 Single-Chip Transceiver

161 of 233

Register Name:

HDLC.RSRIE

Register Description:

HDLC Receive Status Register Interrupt Enable

Register Address:

0B8h

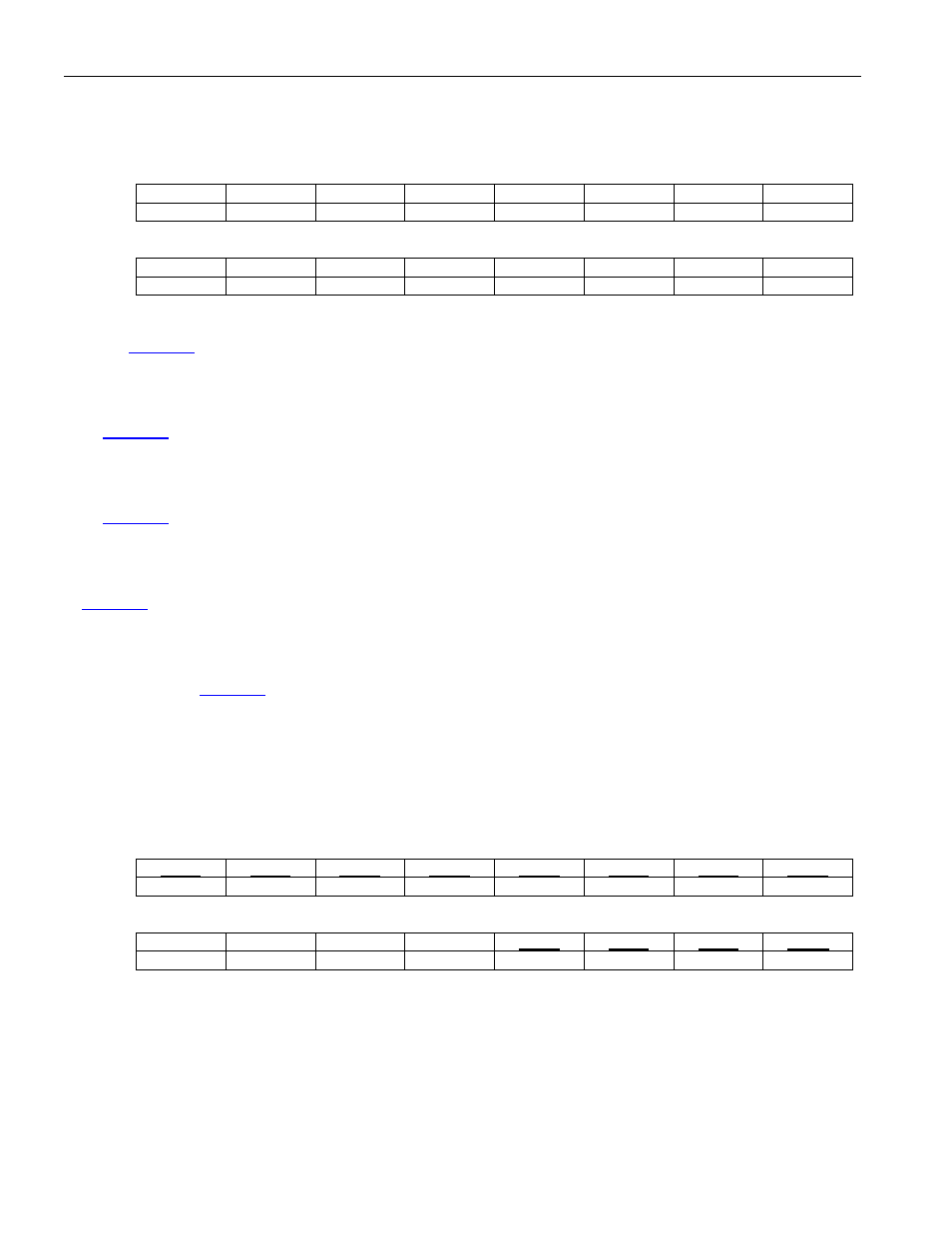

Bit

# 15 14 13 12 11 10 9 8

Name

-- -- -- -- -- -- -- --

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name RFOIE --

-- RPEIE RPSIE RFFIE -- RHDAIE

Default

0 0 0 0 0 0 0 0

Bit 7: Receive FIFO Overflow Interrupt Enable (RFOIE) – This bit enables an interrupt if the RFOL bit is set and

the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 4: Receive Packet End Interrupt Enable (RPEIE) – This bit enables an interrupt if the RPEL bit is set and the

bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 3: Receive Packet Start Interrupt Enable (RPSIE) – This bit enables an interrupt if the RPSL bit is set and the

bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 2: Receive FIFO Full Interrupt Enable (RFFIE) – This bit enables an interrupt if the RFFL bit is set and the bit

in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Bit 0: Receive HDLC Data Available Interrupt Enable (RHDAIE) – This bit enables an interrupt if the RHDAL bit

is set and the bit in

.PSRIE[4:1] that corresponds to this port is set.

0 = interrupt disabled

1 = interrupt enabled

Register Name:

HDLC.RFDR

Register Description:

HDLC Receive FIFO Data Register

Register Address:

0BCh

Bit

# 15 14 13 12 11 10 9 8

Name RFD7 RFD6 RFD5 RFD4 RFD3 RFD2 RFD1 RFD0

Default

X X X X X X X X

Bit

# 7 6 5 4 3 2 1 0

Name

-- -- -- --

RPS2 RPS1 RPS0 RFDV

Default

0 0 0 0 X X X 0

Note: The FIFO data and status are updated when the Receive FIFO Data (RFD[7:0]) is read (upper byte read).

When this register is read eight bits at a time, a read of the lower byte will reflect the status of the next read of the

upper byte, and reading the upper byte when RFDV=0 may result in a loss of data.

Bits 15 to 8: Receive FIFO Data (RFD[7:0]) – These eight bits are the packet data stored in the Receive FIFO.

RFD[7] is the MSB, and RFD[0] is the LSB. If bit reordering is disabled, RFD[0] is the first bit received, and RFD[7]

is the last bit received. If bit reordering is enabled, RFD[7] is the first bit received, and RFD[0] is the last bit

received.