Rainbow Electronics DS2151Q User Manual

Rainbow Electronics Communication

E

Copyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

DS2151Q

T1 Single–Chip Transceiver

DS2151Q

022697 1/46

FEATURES

•

Complete DS1/ISDN–PRI transceiver functionality

•

Line interface can handle both long and short haul

trunks

•

32–bit or 128–bit jitter attenuator

•

Generates DSX–1 and CSU line build outs

•

Frames to D4, ESF, and SLC–96

R

formats

•

Dual onboard two–frame elastic store slip buffers that

connect to backplanes up to 8.192 MHz

•

8–bit parallel control port that can be used on either

multiplexed or non–multiplexed buses

•

Extracts and inserts Robbed–Bit signaling

•

Detects and generates yellow and blue alarms

•

Programmable output clocks for Fractional T1

•

Fully independent transmit and receive functionality

•

Onboard FDL support circuitry

•

Generates and detects CSU loop codes

•

Contains ANSI one’s density monitor and enforcer

•

Large path and line error counters including BPV, CV,

CRC6, and framing bit errors

•

Pin compatible with DS2153Q E1 Single–Chip Trans-

ceiver

•

5V supply; low power CMOS

•

Industrial grade version (–40

°

C to +85

°

C) available

(DS2151QN)

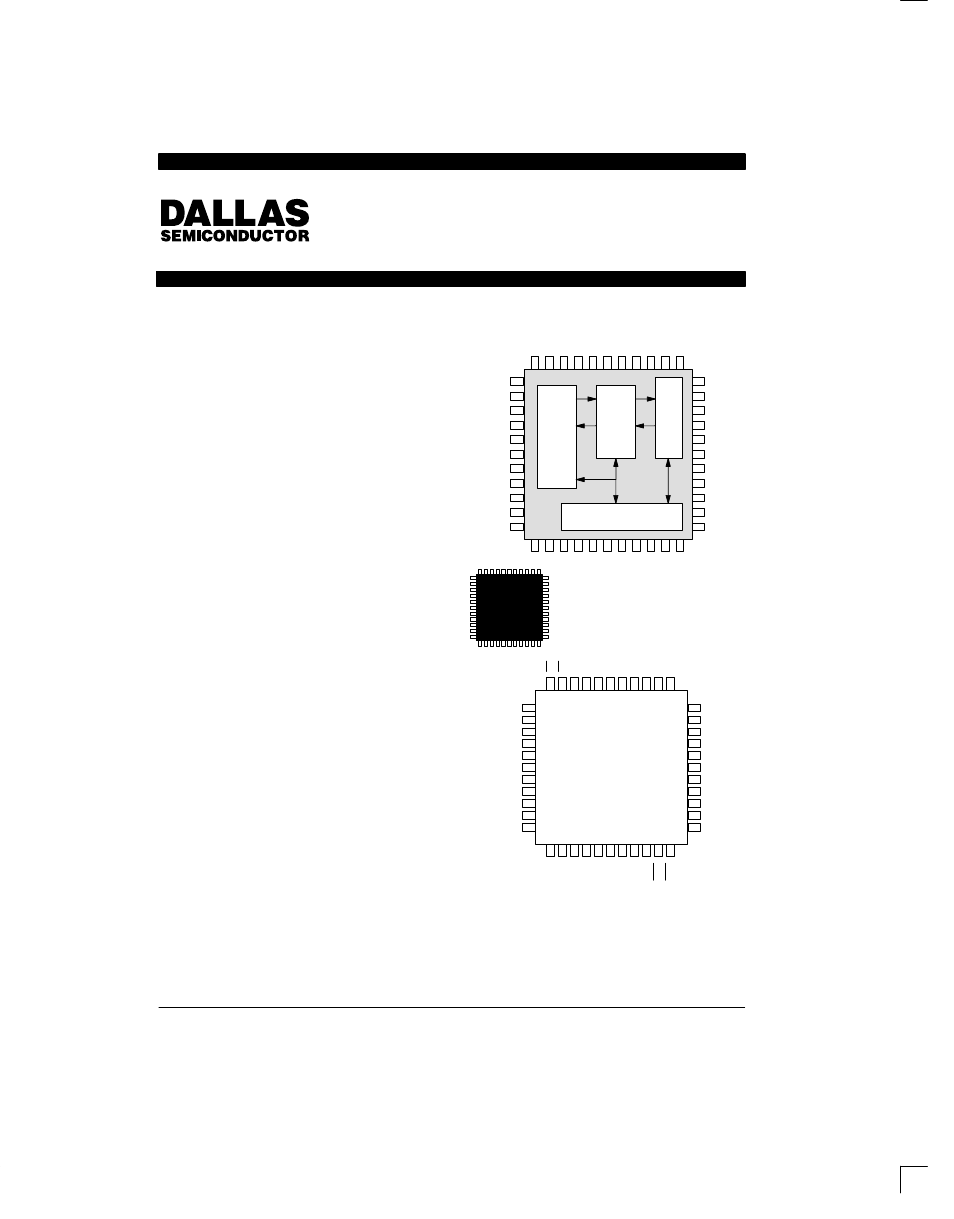

PIN ASSIGNMENT

LONG & SHOR

T

HAUL

LINE INTERF

ACE

PARALLEL CONTROL

PORT

FRAMER

ELASTIC ST

ORES

Functional Blocks

7

8

9

10

11

12

13

14

15

16

17

39

38

37

36

35

34

33

32

31

30

29

18

19

20

21

22

23

24

25

26

27

28

6

5

4

3

2

1

44

43

42

41

40

TSER

TCLK

DVDD

TSYNC

TLINK

TLCLK

TCHBLK

TRING

TVDD

TVSS

TTIP

ALE

WR

RLINK

RLCLK

DVSS

RCLK

RCHCLK

RSER

RSYNC

RLOS/LOTC

SYSCLK

RCHBLK

ACLKI

BTS

R

TIP

RRING

R

VDD

R

VSS

XT

AL1

XT

AL2

INT1

INT2

CS

RD

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

TCHCLK

DALLAS

DS2151Q

T1 SCT

Actual Size of

44–pin PLCC

DESCRIPTION

The DS2151Q T1 Single–Chip Transceiver (SCT) con-

tains all of the necessary functions for connection to T1

lines whether they be DS–1 long haul or DSX–1 short

haul. The clock recovery circuitry automatically adjusts

to T1 lines from 0 feet to over 6000 feet in length. The

device can generate both DSX–1 line build outs as well

as CSU build outs of –7.5 dB, –15 dB, and –22.5 dB.

The onboard jitter attenuator (selectable to either 32 bits