Port.cr1, T bit – Rainbow Electronics DS3170 User Manual

Page 134

DS3170 DS3/E3 Single-Chip Transceiver

134 of 233

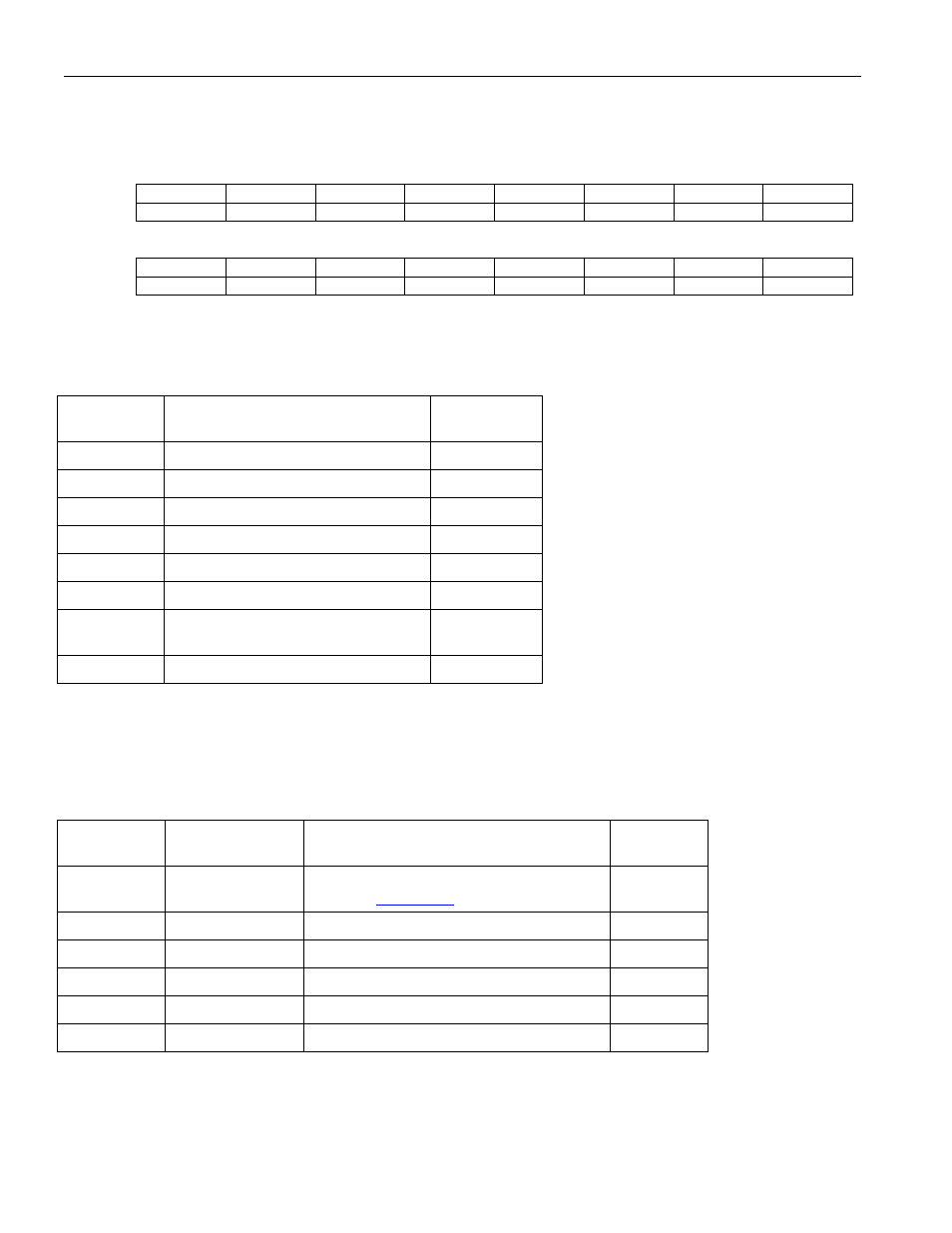

Register Name:

PORT.CR1

Register Description:

Port Control Register 1

Register Address:

040h

Bit

# 15 14 13 12 11 10 9 8

Name

RESERVED

PAIS2 PAIS1 PAIS0 LAIS1 LAIS0 BENA

RESERVED

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name TMEI MEIM -- PMUM PMU PD RSTDP RST

Default

0 0 -- 0 0 1 1 0

Bits 14 to 12: Payload AIS Select [2:0] (PAIS[2:0]). This bit controls when an unframed all ones signal is forced

on the receive data path after the receive framer and payload loopback mux. Default: Payload AIS always sent.

When LLB(no DLB) or PLB active

When OOF, LOS. LLB (no DLB), or

PLB active

Bits 11 to 10: Line AIS Select [1:0] (LAIS[1:0). These bits control when a DS3 framed AIS or an unframed all

ones signal is to be transmitted on TPOS/TNEG and/or TXP/TXN. The signal on TPOS/TNEG can be AMI or

unipolar. This signal is sent even when in diagnostic loopback and always over-rides signals from the framers.

Default: AIS sent if DLB is enabled.

Automatic AIS when DLB is enabled

Automatic AIS when DLB is enabled

Bit 9: BERT Enable (BENA). This bit is used to enable the transmit BERT logic; the receive BERT is always

enabled. The BERT pattern will replace the the system interface datastream (TSER) into the payload datastream.

0 = Tranmit BERT logic disabled and powered down