Register bit descriptions, E3g751.tcr – Rainbow Electronics DS3170 User Manual

Page 184

DS3170 DS3/E3 Single-Chip Transceiver

184 of 233

11.9.3.2 Register Bit Descriptions

Register Name:

E3G751.TCR

Register Description:

E3 G.751 Transmit Control Register

Register Address:

118h

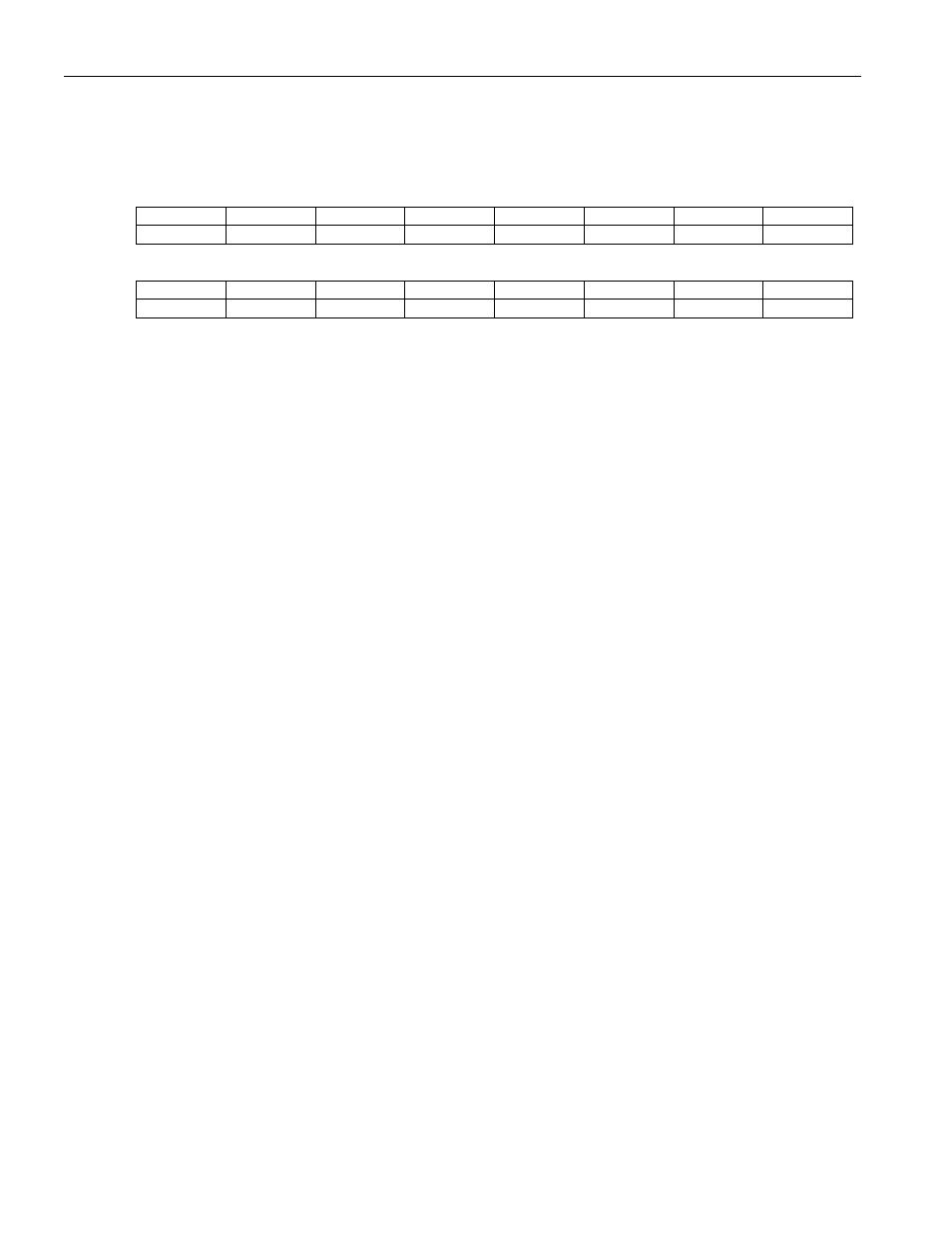

Bit

# 15 14 13 12 11 10 9 8

Name

Reserved --

-- Reserved

Reserved

Reserved

TNBC1

TNBC0

Default

0 0 0 0 0 0 0 0

Bit

# 7 6 5 4 3 2 1 0

Name -- --

Reserved

Reserved

TABC1

TABC0

TFGD

TAIS

Default

0 0 0 0 0 0 0 0

Bits 9 to 8: Transmit N Bit Control (TNBC[1:0]) – These two bits control the source of the N bit.

00 = 1

01 = transmit data from HDLC controller.

10 = transmit data from FEAC controller.

11 = 0

Note: If TNBC[1:0] is 10 and TABC[1:0] is 01, both the N bit and A bit will carry the same transmit FEAC controller

(one bit per frame period), however, the N bit and A bit in the same frame may or may not be equal.

Bits 3 to 2: Transmit A Bit Control (TABC[1:0]) – These two bits control the source of the A bit.

00 = automatically generated based upon received E3 alarms.

01 = transmit from the FEAC controller.

10 = 0

11 = 1

Note: If TABC[1:0] is 01 and TNBC[1:0] is 10, both the A bit and N bit will carry the same transmit FEAC controller

(one bit per frame period), however, the A bit and N bit in the same frame may or may not be equal.

Bit 1: Transmit Frame Generation Disable (TFGD) –

0 = Transmit Frame Generation is enabled

1 = Transmit Frame Generation is disabled; E3 overhead positions in the incoming E3 payload will

be passed through to error insertion. Note: The E3 overhead periods can still be overwritten by by

error insertion, overhead insertion, or AIS generation.

Bit 0: Transmit Alarm Indication Signal (TAIS) – When 0, the normal signal is transmitted. When 1, the output

E3 data stream is forced to all ones (AIS).