Jtag interface ac characteristics, Jtag i, Nterface – Rainbow Electronics DS3170 User Manual

Page 232: Ac c, Haracteristics, Table 17-14. jtag interface timing

DS3170 DS3/E3 Single-Chip Transceiver

232 of 233

17.6 JTAG Interface AC Characteristics

All AC timing characteristics are specified with a 50 pF capacitive load on JTDO pin and 25 pF capacitive load on

all other digital output pins, V

IH

= 2.4V and V

IL

= 0.8. The voltage threshold for all timing measurements is VDD/2.

The voltage threshold for all timing measurements is VDD/2. The generic timing definitions shown in

, and

apply to this interface

.

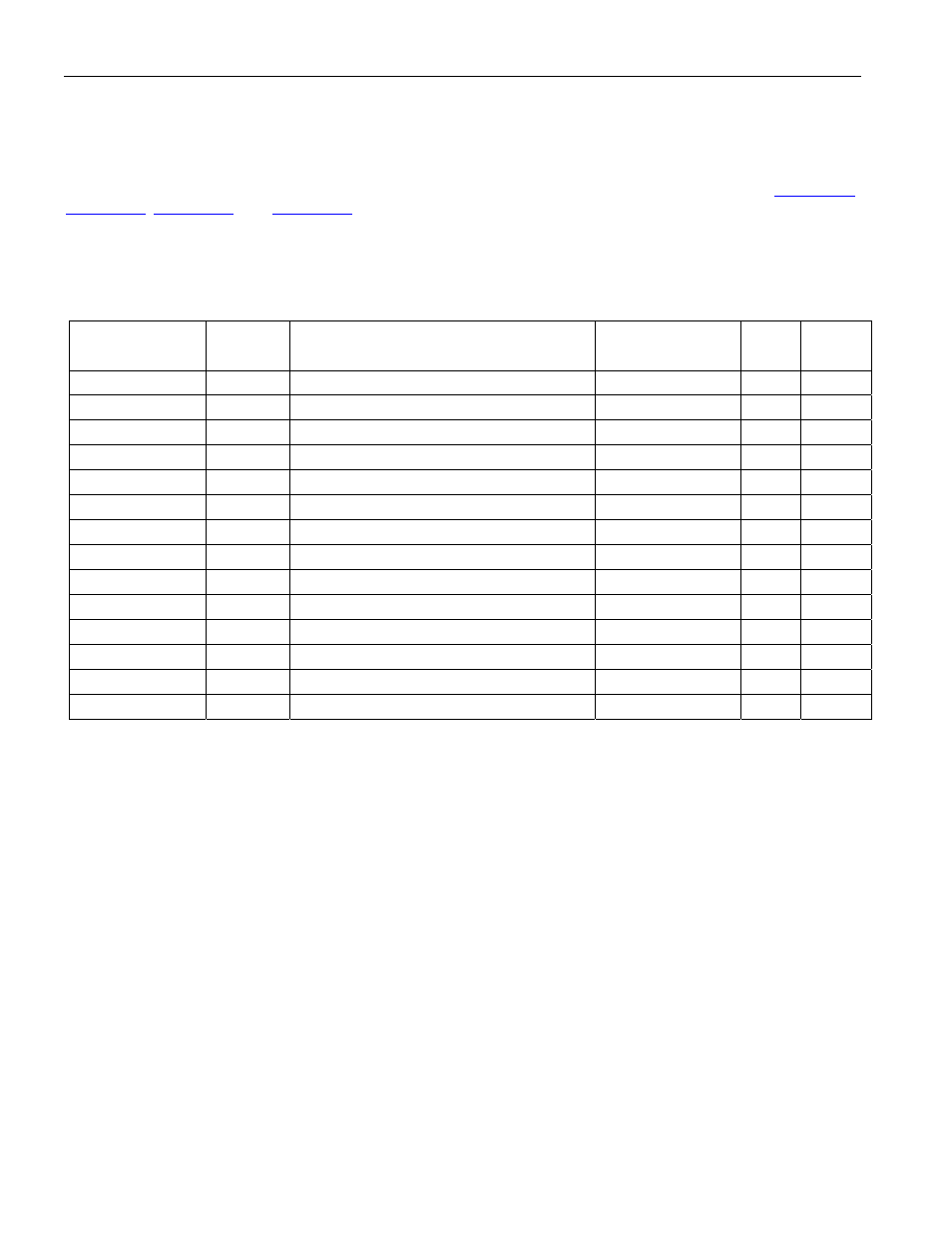

Table 17-14. JTAG Interface Timing

(V

DD

= 3.3V

±5%, T

j

= -40°C to +125°C.)

SIGNAL

NAME(S)

SYMBOL DESCRIPTION MIN

TYP

MAX

UNITS NOTES

JTCLK f1

Clock Frequency (1/t1)

0 10

MHz

JTCLK

t2

Clock High or Low Period

20

ns

JTCLK t3

Rise/Fall

Times

5

ns

JTMS and JTDI

t5

Hold Time from JTCLK Rising Edge

10

ns

JTMS and JTDI

t6

Setup Time to JTCLK Rising Edge

10

ns

JTDO

t7

Delay from JTCLK Falling Edge

0

20

ns

JTDO

t8

Delay out of Hi Z from JTCLK Falling Edge

0

20

ns

JTDO

t9

Delay to Hi Z from JTCLK Falling Edge

0

20

ns

Any digital output

t7

Delay from JTCLK Falling Edge

0

20

ns

1

Any digital output

t7

Delay from JTCLK Rising Edge

0

20

ns

2

Any digital output

t8

Delay out of Hi Z from JTCLK Falling Edge

0 20 ns 1

Any digital output

t9

Delay into Hi Z from JTCLK Falling Edge

0

20

ns

1

Any digital output

t8

Delay out of Hi Z from JTCLK Rising Edge

0

20

ns

2, 3

Any digital output

t9

Delay into Hi Z from JTCLK Rising Edge

0

20

ns

2, 3

Note 1:

Change during Update-DR state.

Note 2:

Change during Update-IR state to or from EXTEST mode.

Note 3:

Change during Update-IR state to or from HIZ mode.