2 detailed status in the rcsr – Zilog Z16C30 User Manual

Page 96

5-29

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

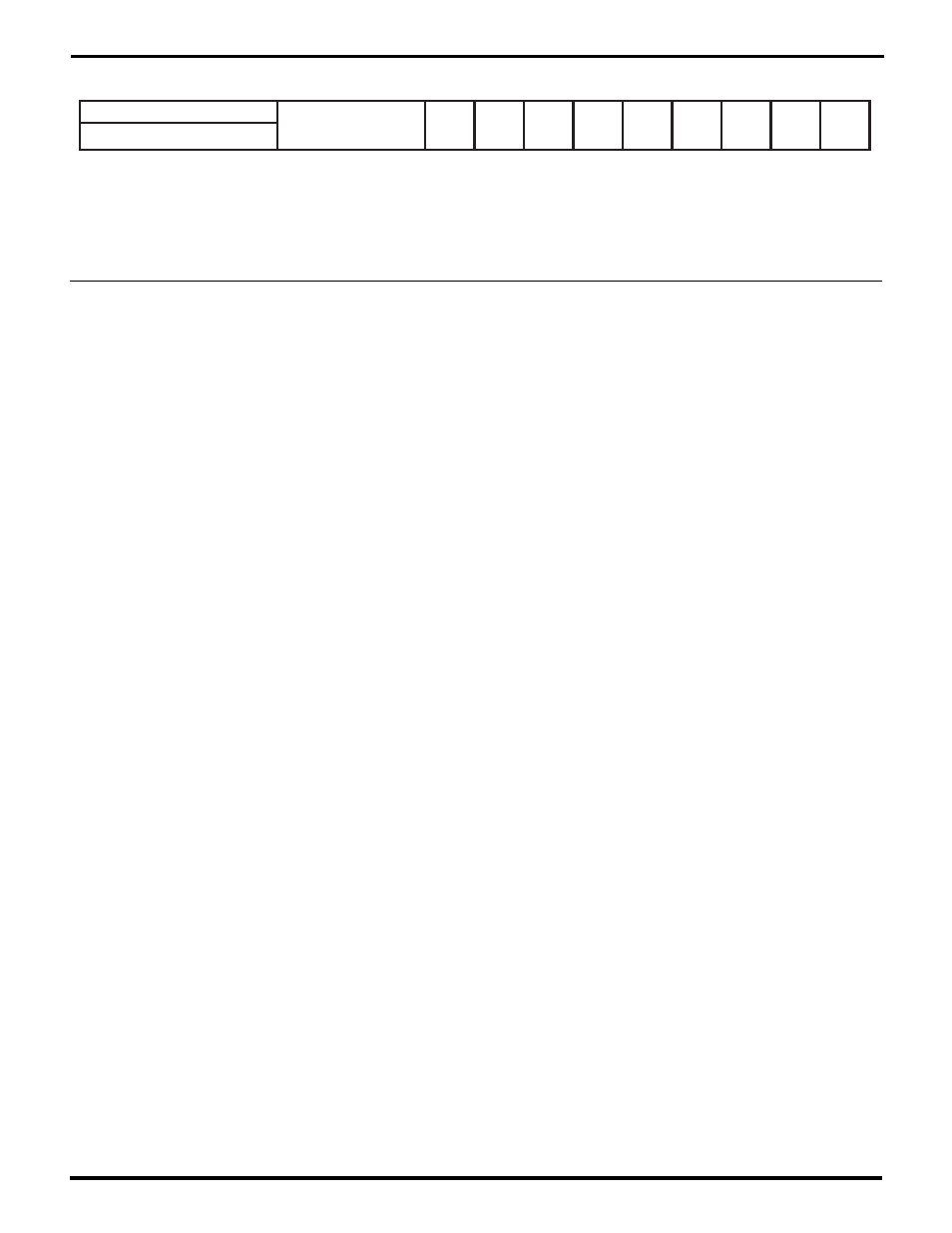

Figure 5-12. The Receive Command/Status Register (RCSR)

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Exited

Hunt

Idle

Rcved

Break

/Abort

Rx

Bound

CRCE

/FE

Abort

/PE

RX

Over

Rx

Avail

RCmd(WO)

2ndBE

1stBE

RxResidue

ShortF/

CVType

5.18.2 Detailed Status in the RCSR

2ndBE:

The USC sets this read-only bit (RCSR15) to 1

when software or an external Receive DMA controller

reads data from the RDR, there are two or more characters

in the RxFIFO, and the Receiver marked the second-oldest

one with one or more of RxBound, Abort/PE, or Rx Overrun

status. (The bit’s name stands for Second Byte Exception.)

A channel clears this bit to 0 when software or the Receive

DMA controller reads data from the RxFIFO/RDR, there are

two or more characters in the RxFIFO, and the Receiver

didn’t mark the second-oldest one with any of these three

conditions. If software or the Receive DMA controller reads

data from the RDR when there’s only one character in it,

this bit is undefined until the next time one of them reads

RDR.

1stBE:

The USC sets the read-only bit (RCSR14) to 1 when

software or an external Receive DMA controller reads data

from the RDR, and the Receiver marked the oldest charac-

ter read with one or more of RxBound, Abort/PE, or Rx

Overrun status. (The bit’s name stands for First Byte

Exception.) A channel clears this bit to 0 when software or

the Receive DMA controller reads data from the RDR, and

the Receiver didn’t mark the oldest character with any of

these three conditions.

ShortF/CVType:

The Receiver queues this bit through the

RxFIFO with each character. RCSR8 may reflect the status

at the time that an RxBound character was read from the

RxFIFO, or the status associated with the oldest 1 or 2

character(s) still in the RxFIFO, as described earlier in this

Status Reporting section. In a stored Receive Status Block

it always represents the status of the preceding RxBound

character.

This bit will be 1 only in HDLC/SDLC and only for charac-

ters that the Receiver also marks with RxBound=1. When

the RxSubMode field (CMR7-4) specifies Address and

possibly Control field processing in HDLC/SDLC mode,

the Receiver sets this bit for the last character of a frame if

it hasn’t come to the end of the specified field(s) by the end

of the frame.

ExitedHunt:

The Receiver sets this bit (RCSR7) in any

mode, when it leaves its Hunt state. In Async modes this

happens right after software enables the Receiver. In

External Sync mode, the Receiver leaves Hunt state when

the Enable/Sync signal on /DCD goes from high to low. In

Monosync, Bisync, or Transparent Bisync mode the Re-

ceiver leaves Hunt state when it recognizes a Sync se-

quence. In HDLC/SDLC mode the Receiver leaves Hunt

state when it recognizes a Flag. In 802.3 (Ethernet) mode,

if software has enabled address checking the Receiver

leaves Hunt state when it matches the Address at the start

of a frame, otherwise it does so after detecting the start bit

at the end of the Preamble.

A channel can request an interrupt when this bit goes from

0 to 1 if the ExitedHunt IA bit in the Receive Interrupt Control

Register (RICR7) is 1. Software must write a 1 to ExitedHunt

to unlatch and clear it, and allow further interrupts if RICR7

is 1; writing a 0 to ExitedHunt has no effect.

IdleRcved:

The Receiver sets this bit (RCSR6) when it

samples RxD as one for 15 consecutive RxCLKs in

HDLC/SDLC mode, or for 16 consecutive RxCLKs in any

other mode. A channel can request an interrupt when this

bit goes from 0 to 1 if the IdleRcved IA bit in the Receive

Interrupt Control Register (RICR6) is 1. Software must write

a 1 to IdleRcved to unlatch it, and to allow further interrupts

if RICR6 is 1; writing a 0 has no effect. A channel doesn’t

actually clear RCSR6 until software has written a 1 to

unlatch it, and RxD has gone to 0 to end the idle condition.

(IdleRcved isn’t useful in Async modes that use a 16x, 32x,

or 64x clock. In these cases keep RICR6=0 to avoid

interrupts, and ignore RCSR6.)

Break/Abort:

The Receiver sets this bit (RCSR5) in an

asynchronous mode when it detects a Break condition,

that is, when it samples the Stop bit of a character as 0, and

all the preceding data bits (and the parity bit if any) have

also been 0. It sets the bit in HDLC/SDLC mode when it

detects seven consecutive ones, i.e., an Abort or Go

Ahead sequence.

UM009402-0201