Zilog Z16C30 User Manual

Page 161

8-6

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

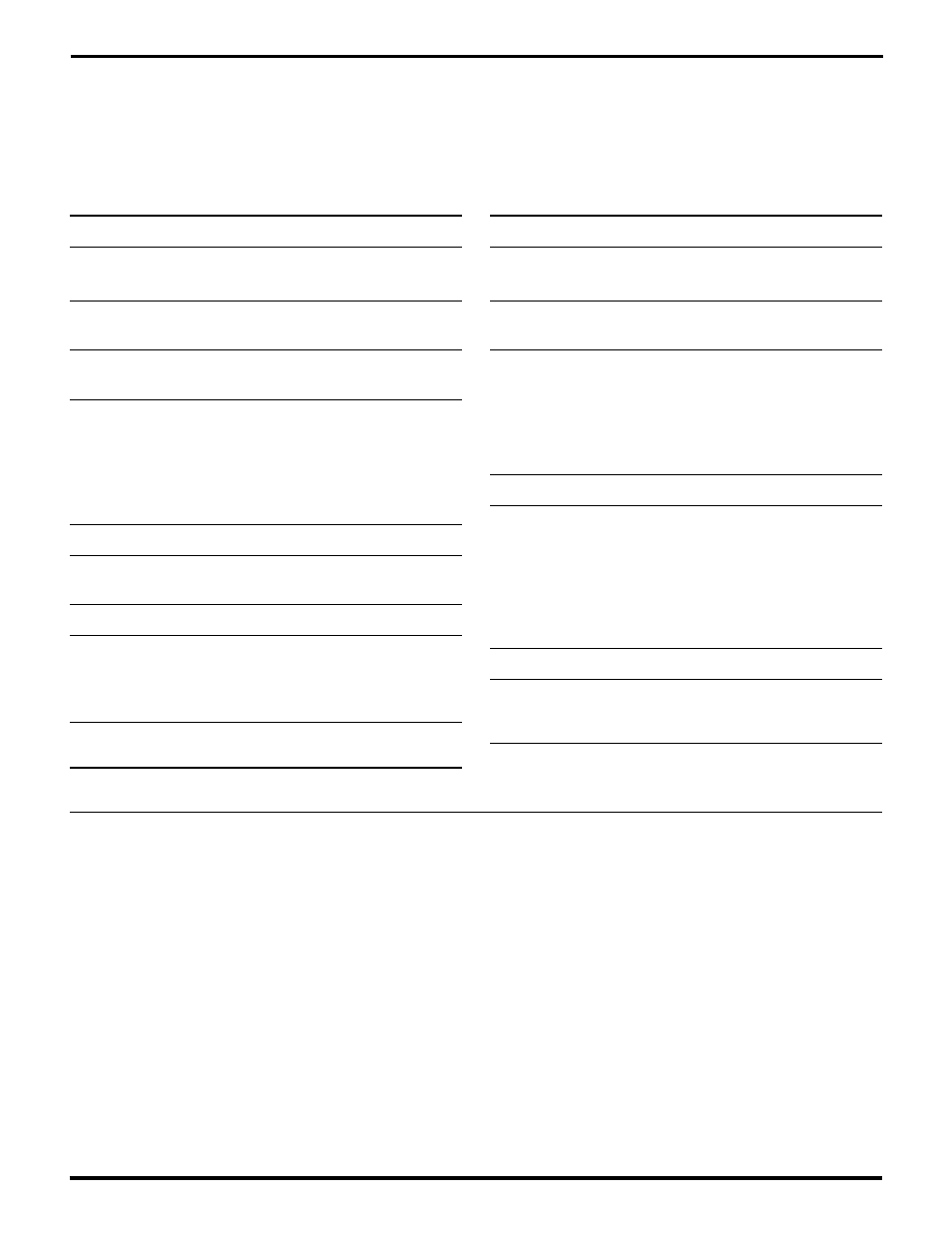

8.7 TEST MODES

The USC includes a facility intended for Zilog’s device

testing, that gives software access to certain internal

signals and registers that are not otherwise accessible.

The low-order bits of the Test Mode Control Register

(TMCR) serve to select which internal signals or registers

are accessed by reading (or in some cases writing) the

Test Mode Data Register (TMDR). The choices are as

follows:

TMCR4-0

Signals/Register Selection

R/W Status

00001

TMDR15-8: Rx shift register, MSbyte

RO

TMDR 7-0: Tx shift register, MSbyte

RO

00010

TMDR15-8: Rx CRC checker, LSbyte

RO

TMDR 7-0: Tx CRC generator, LSbyte

RO

00011

TMDR15-8: Rx CRC checker, bits 15-8

RO

TMDR 7-0: Tx CRC generator, bits 15-8

RO

00100

serial side of RxFIFO:

WO

TMDR11:ShortF/CVType status bit

WO

TMDR10:Abort/PE status bit

WO

TMDR9:RxBound status bit

WO

TMDR8:CRC Error status bit

WO

TMDR7-0:data character

WO

00101

Clock MUX outputs (see Figure 8-1 below)

RO

00110

TMDR12-8: CTR1 value

RO

TMDR4-0: CTR0 value

RO

00111

Clock MUX inputs (see Figure 8-2 below)

RO

01000

TMDR15:DPLL Adjust

RO

TMDR14:DPLL Shorten/Extend

RO

TMDR13: DPLL One/Two

RO

TMDR12-8: DPLL State

RO

01001

TMDR15-8: Rx shift register, LSbyte

RO

TMDR 7-0: Tx shift register, LSbyte

RO

TMCR4-0

Signals/Register Selection

R/W Status

01010

TMDR15-8: Rx CRC checker, bits 23-16

RO

TMDR 7-0: Tx CRC generator, bits 23-16

RO

01011

TMDR15-8: Rx CRC checker, bits 31-24

RO

TMDR 7-0: Tx CRC generator, bits 31-24

RO

01100

serial side of TxFIFO:

RO

TMDR10:EOF/EOM bit

RO

TMDR9:CRC enable bit

RO

Transparent Bisync: insert DLE

RO

Nine-Bit mode: Address/Data

RO

TMDR7-0:RxFIFO, data character

RO

01110

I/O and Misc status (see Figure 8-3 below)

WO

01111

internal interrupt daisy chain:

RO

TMDR13:Rx Status IEO

RO

TMDR12Rx Data IEO

RO

TMDR11:Tx Status IEO

RO

TMDR10:Tx Data IEO

RO

TMDR9:I/O Pin IEO

RO

TMDR8:Misc IEO

RO

10110

Receive Count Holding Register (RCHR)

RO

11111

Device Version Code:

RO

4453

Device manufactured before June 93

RO

4D44

Device manufactured after June 93

RO

software-programmable wait state generator that can ex-

tend accesses to TMDR but not penalize performance for

other USC register accesses.

The TMDR is designed as a device test facility that a tester

can read or write 16 bits at a time. Reading its "MSByte"

address returns the contents of the "LSbyte". Therefore the

MS 8 bits of the TMDR cannot be accessed over an 8-bit

bus.

Some of this information may be of use to software.

However, the hardware access time for reading the TMDR

is considerably longer than for other USC registers. (See

the Product Description document for details.)

If software needs to read any of the above Test Mode

information, the hardware design must provide more time

for the data lines to become valid, than would otherwise be

necessary. This may require the injection of more “wait

states” into such read cycles than would be needed for

other registers. In some cases the best solution is a

UM009402-0201