Zilog Z16C30 User Manual

Page 191

8-36

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

TxEncode

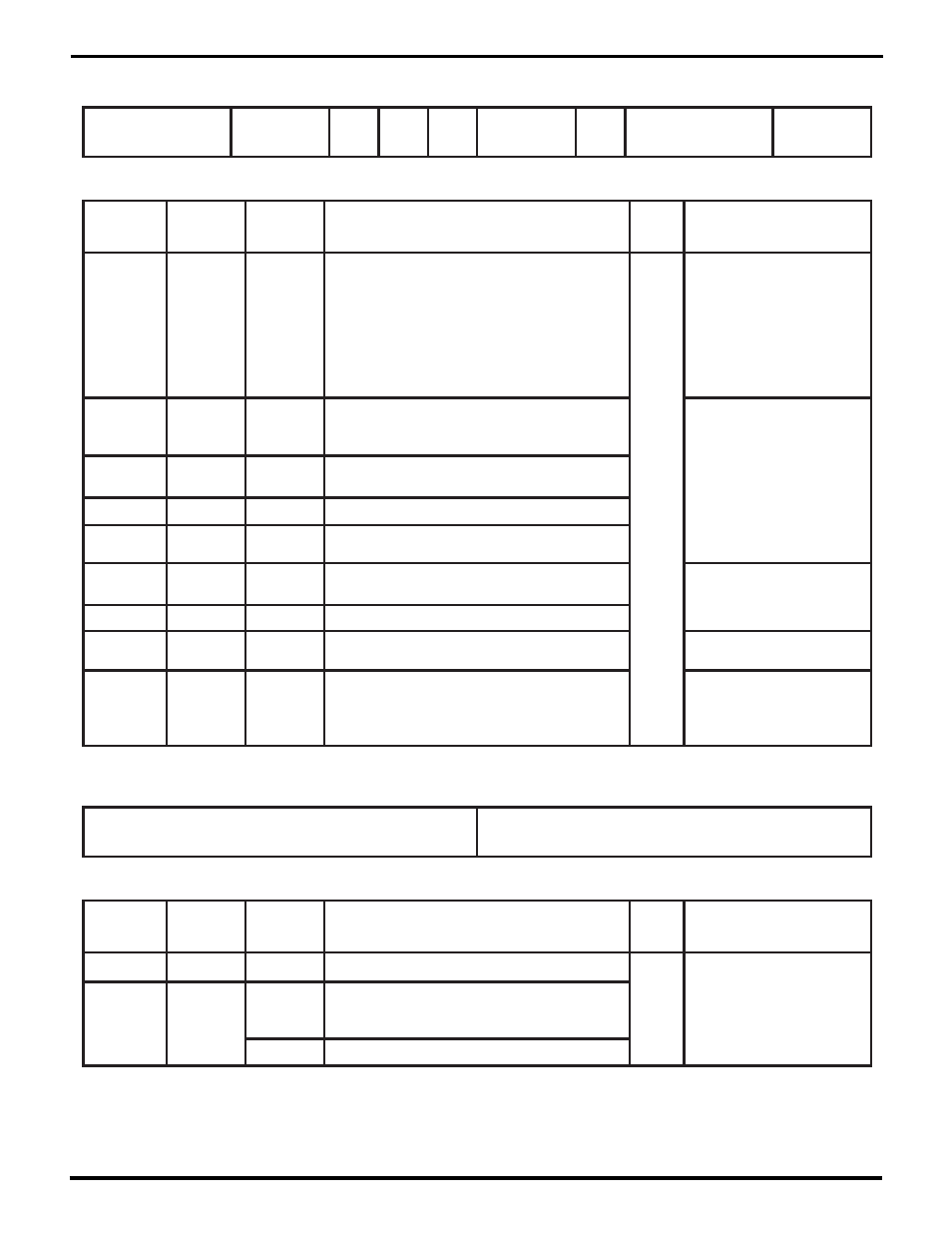

Transmit Mode Register (TMR)

Register Address 0 b 11001

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

TxPar

Enab

TMR15-13

TxCRCType

TxCRC

Start

TxCRC

Enab

TxCRC

atEnd

TxParType

TxLength

TxEnable

TxEncode

000=don't encode TxD ("NRZ");

001=invert polarity of TxD ("NRZB");

010=encode TxD NRZI-Mark;

011=encode TxD NRZI-Space;

100=encode TxD Biphase-Mark (FM1);

101=encode TxD Biphase-Space (FM0);

110=encode TxD Biphase-Level (Manchester);

111=encode TxD Differential Biphase-Level

RW

4: Data Formats and

Encoding

TMR12-11

TxCRCType

00=use 16-bit CRC-CCITT for Tx;

01=use CRC-16 for Tx;

10=use 32-bit Ethernet CRC for Tx

5: Cyclic Redundancy

Checking

Sync

TMR10

TxCRCStart

0=start Transmit CRC generator as all zeros;

1=all ones

Sync

TMR9

TxCRCEnab

1=include Transmit characters in CRC

Sync

TMR8

TxCRCat

End

1=send accumulated CRC at EOF/EOM

Sync

TMR7-6

TxParType

00=Transmit Parity Even; 01=Odd;

10=Zero (Space); 11=One (Mark)

5: Parity Checking

TMR5

TxParEnab

1=accumulate and send Parity bits

TMR4-2

TxLength

000=send eight bit characters;

001-111=send 1-7 bit characters

5: The Mode Registers:

Character Length

TMR1-0

TxEnable

00=disable Transmitter (immediately);

01=disable Tx at end of message/frame/char;

10=enable Tx unconditionally;

11=auto-enable Tx per /CTS pin

5: The Mode Registers:

Enabling and Disabling

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Transmit Sync Register (TSR)

Register Address 0 b 11100

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

RSR15-8

Transmit SYN1

Transmit Sync or SYN0

Second half of Transmit sync (SYN1)

WR

4: Monosync and Bisync

Modes

4: Slaved Monosync Mode

Bisync

RSR7-0

Transmit Sync character

Monosync,

Slaved

Monosync

First half of Transmit sync (SYN0)

Bisync

RW = Read/Write, RO = Read Only, WO = Write Only – for other codes see p. 8-10.

UM009402-0201