Zilog Z16C30 User Manual

Page 37

2-11

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

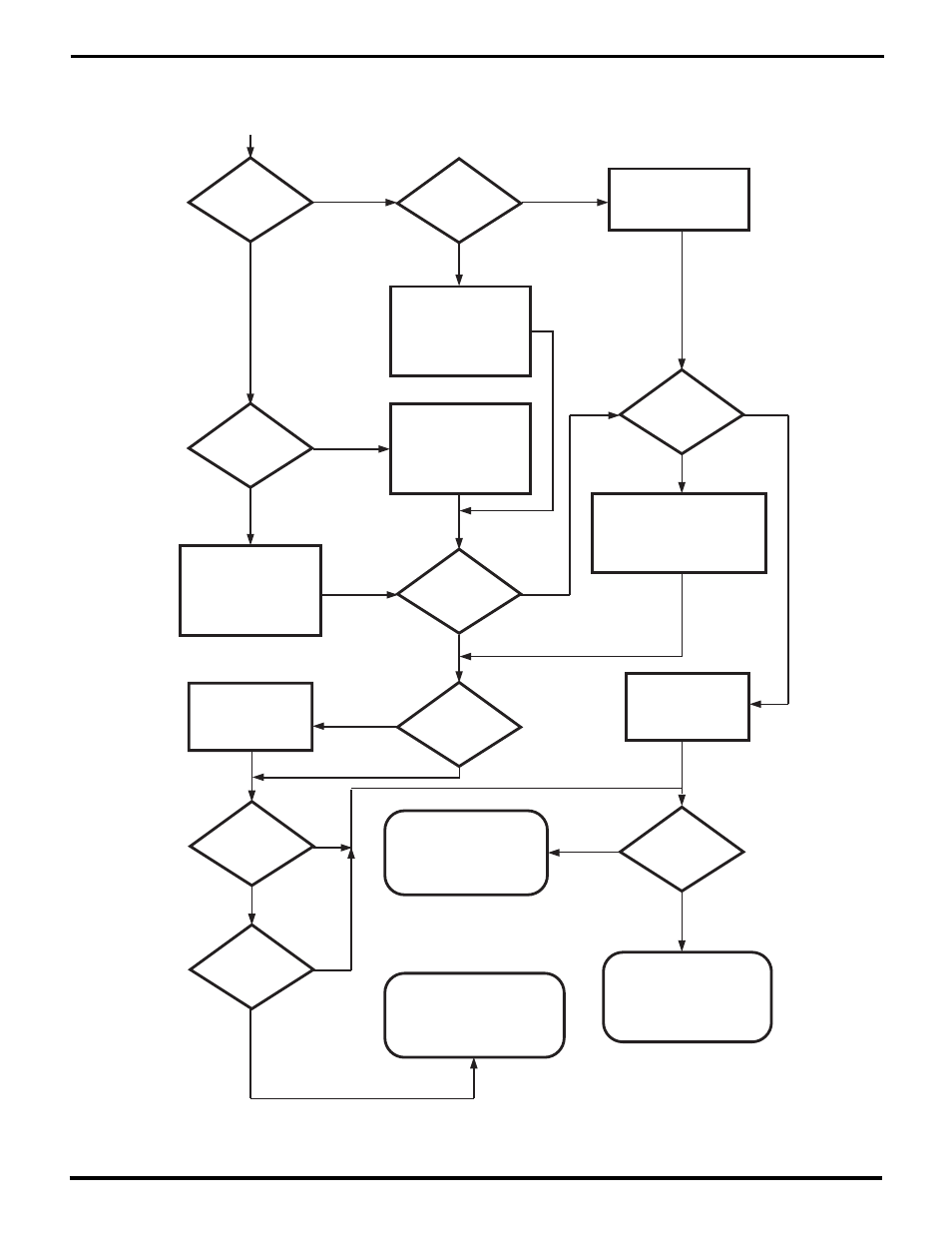

Figure 2-9. USC Register Addressing

Activity

on /AS after

Reset?

SEPAD

(BCR15)

Start: Host Cycle

with /CS Low -

which register to R/W?

(No Separate

Ad)

0

(Non-Mux'ed

Bus)

No

Capture iA/B:=A//B,

iD/C:=D//C at fall

of /DS, /RD, or /WR

Capture iA/B:=A/B,

B//W:=AD6, RegAd:=

AD5-0, iD/C:=D//C

at rise of /AS

(Mux'ed Bus)

Yes

Activity

on /AS after

Reset?

Capture iA//B:=A//B

RegAd = AD13-AD8,

iD/C = D//C

at rise of /AS

(Mux'ed Bus)

Yes

(Separate Addr)

1

Capture iA//B:=A//B,

RegAd = AD13-AD8,

iD/C = D//C at fall

of /DS, /RD, or /WR

(Non-Mux'ed Bus)

No

RegAd = 0?

Yes

iD//C

High/1

(Serial)

(Control)

Low/0

Using channel iA//B,

B//W:=CCAR6;

RegAd:=CCAR5-0;

then CCAR5-0:=0

No

16-Bit

(BCR2)

B//W = Not 16-Bit

(BCR2)

Read

or

Write?

Force B//W

: = 1 (Byte)

0

Write 1 or 2 char-

acters to channel

(iA//B)'s TxFIFO,

depending on B//W

Write

iD/C

RegAd

= 1x000?

Read 1 or 2 cha-

racters from channel

(iA//B)'s RxFIFO,

depending on B//W

Access the register

in Channel (iA//B)

selected by RegAd,

8/16 bits per B//W

1

High/1

(Data)

Low /0

(Control)

Yes

No

Read

UM009402-0201