Zilog Z16C30 User Manual

Page 174

8-19

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

IOP

IUS

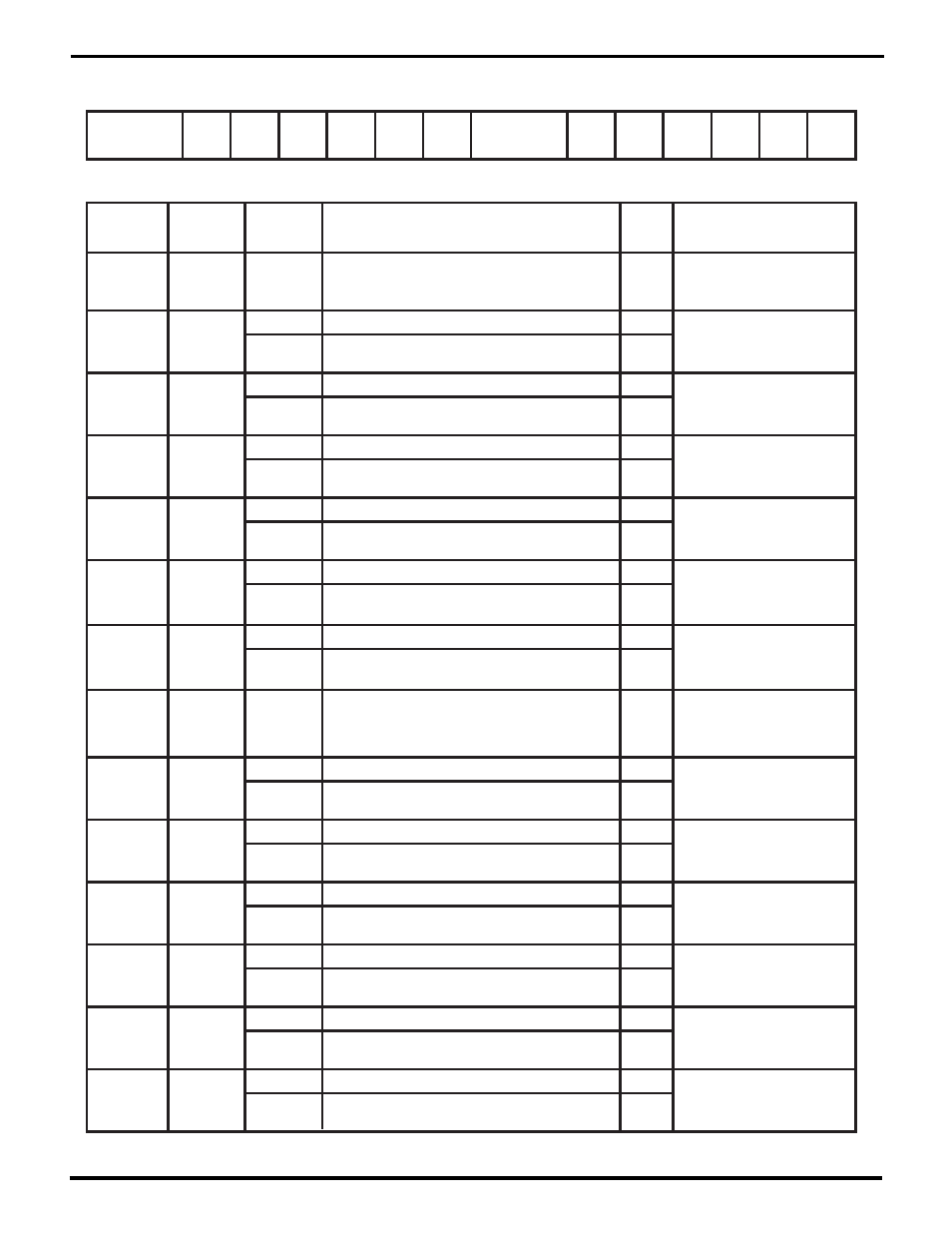

Daisy Chain Control Register (DCCR)

Register Address 0 b 01101

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

Misc

IP

DCCR15-14

IOP

IP

TD

IP

TS

IP

RD

IP

RS

IP

IP Op

(WO)

TD

IUS

TS

IUS

RD

IUS

RS

IUS

IUS Op

(WO)

IUS Op

Write

0x=no operation;

10=clear IUS bits selected by 1s in DCCR13-8;

11=set IUS bits selected by 1s in DCCR13-8

WO

7: Interrupt Pending and

Under Service Bits

DCCR13

RS IUS

Read

1=Receive Status interrupt under service

RO

7: Interrupt Pending and

Under Service Bits

7: Rx Status Interrupt Sour-

ces and IA Bits

Write

1=set or clear Receive Status IUS per IUS Op;

0=no change

WO

DCCR12

RD IUS

Read

1=Receive Data interrupt under service

RO

7: Interrupt Pending and

Under Service Bits

7: Rx Data Interrupts

Write

1=set or clear Receive Data IUS per IUS Op;

0=no change

WO

DCCR11

TS IUS

Read

1=Transmit Status interrupt under service

RO

7: Interrupt Pending and

Under Service Bits

7: Tx Status Interrupt Sour-

ces and IA Bits

Write

1=set or clear Transmit Status IUS per IUS Op;

0=no change

WO

DCCR10

TD IUS

Read

1=Transmit Data interrupt under service

RO

7: Interrupt Pending and

Under Service Bits

7: Transmit Data Interrupts

Write

1=set or clear Transmit Data IUS per IUS Op;

0=no change

WO

DCCR9

IOP IUS

Read

1=I/O Pin interrupt under service

RO

7: Interrupt Pending and

Under Service Bits

7: I/O Pin Interrupt Sources

and IA Bits

Write

1=set or clear I/O Pin IUS per IUS Op;

0=no change

WO

DCCR8

Misc IUS

Read

1=Miscellaneous interrupt under service

RO

7: Interrupt Pending and

Under Service Bits

7: Miscellaneous Interrupt

Sources and IA Bits

Write

1=set or clear Miscellaneous per IUS Op;

0=no change

WO

DCCR7-6

IP Op

Write

00=no operation;

01=clear IP and IUS bits sel by 1s in DCCR5-0;

10=clear IP bits selected by 1s in DCCR5-0;

11=set IP bits selected by 1s in DCCR5-0

WO

7: Interrupt Pending and

Under Service Bits

DCCR5

RS IP

Read

1=Receive Status interrupt pending

RO

7: Interrupt Pending and

Under Service Bits

7: Rx Status Interrupt

Sources and IA Bits

Write

WO

1=set or clear Receive Status IP/IUS per IP Op;

0=no change

DCCR4

RD IP

Read

1=Receive Data interrupt pending

RO

7: Interrupt Pending and

Under Service Bits

7: Rx Data Interrupts

Write

WO

1=set or clear Receive Data IP/IUS per IP Op;

0=no change

DCCR3

TS IP

Read

1=Transmit Status interrupt pending

RO

7: Interrupt Pending and

Under Service Bits

7: Tx Status Interrupt

Sources & IA Bits

Write

WO

1=set or clear Transmit Status IP/IUS per IP Op;

0=no change

DCCR2

TD IP

Read

1=Transmit Data interrupt pending

RO

7: Interrupt Pending and

Under Service Bits

7: Transmit Data

Interrupts

Write

WO

1=set or clear Transmit Data IP/IUS per IP Op;

0=no change

DCCR1

IOP IP

Read

1=I/O Pin interrupt pending

RO

7: Interrupt Pending and

Under Service Bits

7: I/O Pin Interrupt

Sources & IA Bits

Write

WO

1=set or clear I/O Pin IP/IUS per IP Op;

0=no change

DCCR0

Misc IP

Read

1=Miscellaneous interrupt pending

RO

7: Interrupt Pending and

Under Service Bits

7: Miscellaneous Interrupt

Sources and IA Bits

Write

WO

1=set or clear Miscellaneous IP/IUS per IP Op;

0=no change

Misc

IUS

RW = Read/Write, RO = Read Only, WO = Write Only – for other codes see p. 8-10.

UM009402-0201