Zilog Z16C30 User Manual

Page 166

8-11

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Reserved (Must be zero)

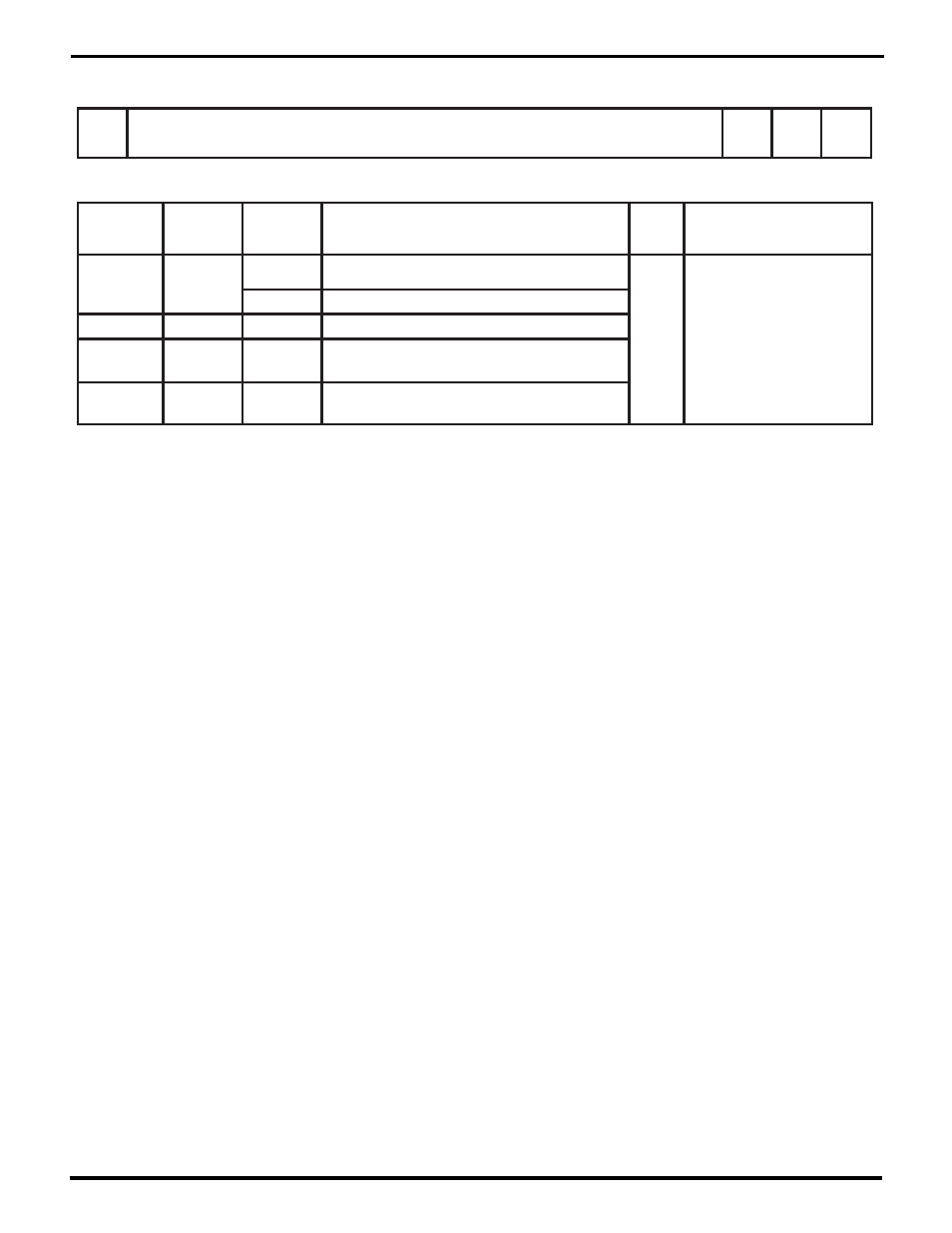

Bus Configuration Register (BCR)

No Address (First Write after /RESET)

SepAd

16Bit

2Pulse

IACK

SRight

A

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

BCR15

SepAd

1 if AD13-8 carry register addresses

WO

2: Bus Configuration Register

8-bit bus

Must be 0

16-bit bus

BCR2

16-Bit

0=8-bit data on AD7-0; 1=16-bit data on AD15-0

BCR1

2PulseIACK

0=one pulse on /PITACK per interrupt

acknowledge; 1 = two pulses (Intel compatible)

BCR0

SRightA

1=use AD6-0 as B/W, RegAddr, U/L

0=use AD7-1

Muxed AD

/PITACK

used

RW = Read/Write, RO = Read Only, WO = Write Only – for other codes see p. 8-10.

UM009402-0201

See also other documents in the category Zilog Sensors:

- S3F94C8 (11 pages)

- S3F80QB (29 pages)

- S3F8S19 (38 pages)

- Z51F6412 (96 pages)

- Z51F6412 (54 pages)

- Z51F6412 (55 pages)

- Z16F6411 (20 pages)

- Z16F6411 (216 pages)

- EZ80F93 (11 pages)

- ZMOT0BSB (314 pages)

- ZMOT0BSB (582 pages)

- EZ80F93 (13 pages)

- Z8F083A (14 pages)

- Z8F2480 (17 pages)

- Z8F082A (18 pages)

- Z8F082A (15 pages)

- Z8F0822 (17 pages)

- Z8F6423 (83 pages)

- Z8F2480 (19 pages)

- Z8F2480 (18 pages)

- Z8F6423 (18 pages)

- Z8F6423 (27 pages)

- Z8F6482 (50 pages)

- EZ80F915 (411 pages)

- EZ80F91NAA (34 pages)

- EZ80F91 (41 pages)

- EZ80L92 (40 pages)

- EZ80L92 (26 pages)

- EZ80L92 (79 pages)

- EZ80F91GA (469 pages)

- eZ80F92 (87 pages)

- EZ80L92 (10 pages)

- Z16FMC6 (520 pages)

- Z8FMC16 (26 pages)

- Z16FMC6 (41 pages)

- ZUSBOPTS (38 pages)

- ZUSBOPTS (59 pages)

- Z16FMC6 (8 pages)

- Z16FMC6 (26 pages)

- ZMOT1AHH (25 pages)

- ZMOT0BSB (34 pages)

- EZ80F915 (78 pages)

- EZ80190 (87 pages)

- EZ80L92 (86 pages)

- EZ80F91GA (127 pages)