4 using /rxreq and /txreq as interrupt requests – Zilog Z16C30 User Manual

Page 131

7-3

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

7.4 USING /RXREQ AND /TXREQ AS INTERRUPT REQUESTS

When an external DMA controller isn’t used to handle the

Receive or Transmit data for a channel, the corresponding

REQ pin isn’t used to output a DMA transfer request. In this

case software can still program the pin as a "DMA request"

output, and the system designer can use the output signal

as another interrupt request instead.

As we will see, software can program “interrupt request

levels” to determine when a FIFO asserts the /INT pin.

These request levels are similar to those discussed in

Chapter 6 for the way the FIFO controls its REQ pin. A

system designer can use /TxREQA, /TxREQB, /RxREQA,

or /RxREQB for another interrupt request line. This is

particularly advantageous in a system in which the host

processor has multiple interrupt request levels, and the

software allows/uses nested interrupts. In such a system,

the REQ pin(s) can be connected to a different request

level than is the /INT pin, so that data interrupts have a

different priority than other kinds of interrupts.

The 'DMA Requests by the Receiver and Transmitter'

section of Chapter 6 describes how a channel asserts the

REQ pin until the software has completely filled the TxFIFO

or emptied the RxFIFO, or until the end of the message/

frame, whichever comes first. This differs from how a

channel asserts its /INT output, and means that an interrupt

service routine must take or provide data until the FIFO is

full or empty or until the end of the frame or message, in

order to avoid immediate re-interruption.

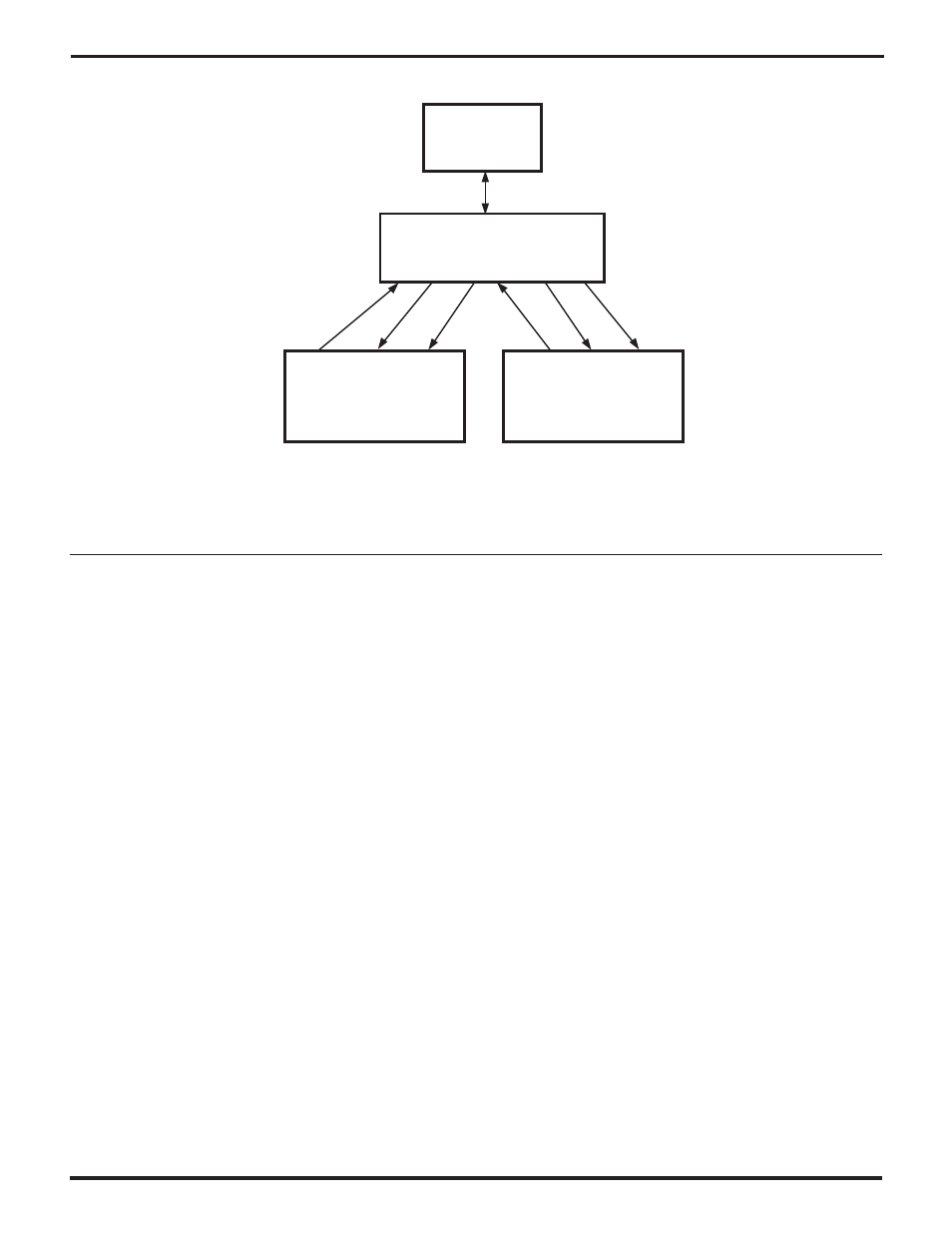

/INT,

/INTB

IEIA,

IEIB

/SITACK

or

/PITACK

IUSC

Other Devices

Interrupt Control Logic

Processor

Figure 7-2. External Interrupt Control

UM009402-0201