4 transmit data interrupts – Zilog Z16C30 User Manual

Page 147

7-19

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

the corresponding bit in the Transmit Command/Status

Register (TCSR) goes from 0 to 1. If an IA bit is 0, the

corresponding TCSR bit has no effect on the IP bit and thus

will not cause interrupts. The setting of the IA bits in TICR

has no direct effect on the TCSR bits.

When software wants to change the IA bits in the TICR after

the register is first initialized, it should write only the LS byte

of the register rather than all 16 bits, to avoid inadvertently

changing a threshold setting in the MS byte.

7.11.4 Transmit Data Interrupts

This interrupt type has only one source, so there’s no need

for an IA bit for it. The interrupt logic sets the

Transmit Data

IP

bit whenever the number of empty character positions

in the TxFIFO is greater than the number programmed as

the “Transmit Data Interrupt Request Level”. If transmitted

data is to be handled by an external Transmit DMA chan-

nel, disable this interrupt by leaving its IE bit 0. (A later

section discusses IE bits.)

To program the Transmit Data Interrupt Request Level, first

write the “Select TICRHi=/INT Level” command ( 0110) to

the TCmd field of the Transmit Command / Status Register

(TCSR15-12). Then write the number of empty character

positions at which the channel should start requesting a

Transmit Data interrupt, minus one, to the MSByte of the

Transmit Interrupt Control Register (TICR). For example, if

the channel should request a Transmit Data interrupt when

its 32-byte TxFIFO has only four characters left in it, write

hex 60 to TCSR15-8, then write decimal 27 (hex 1B) to

TICRI5-8.

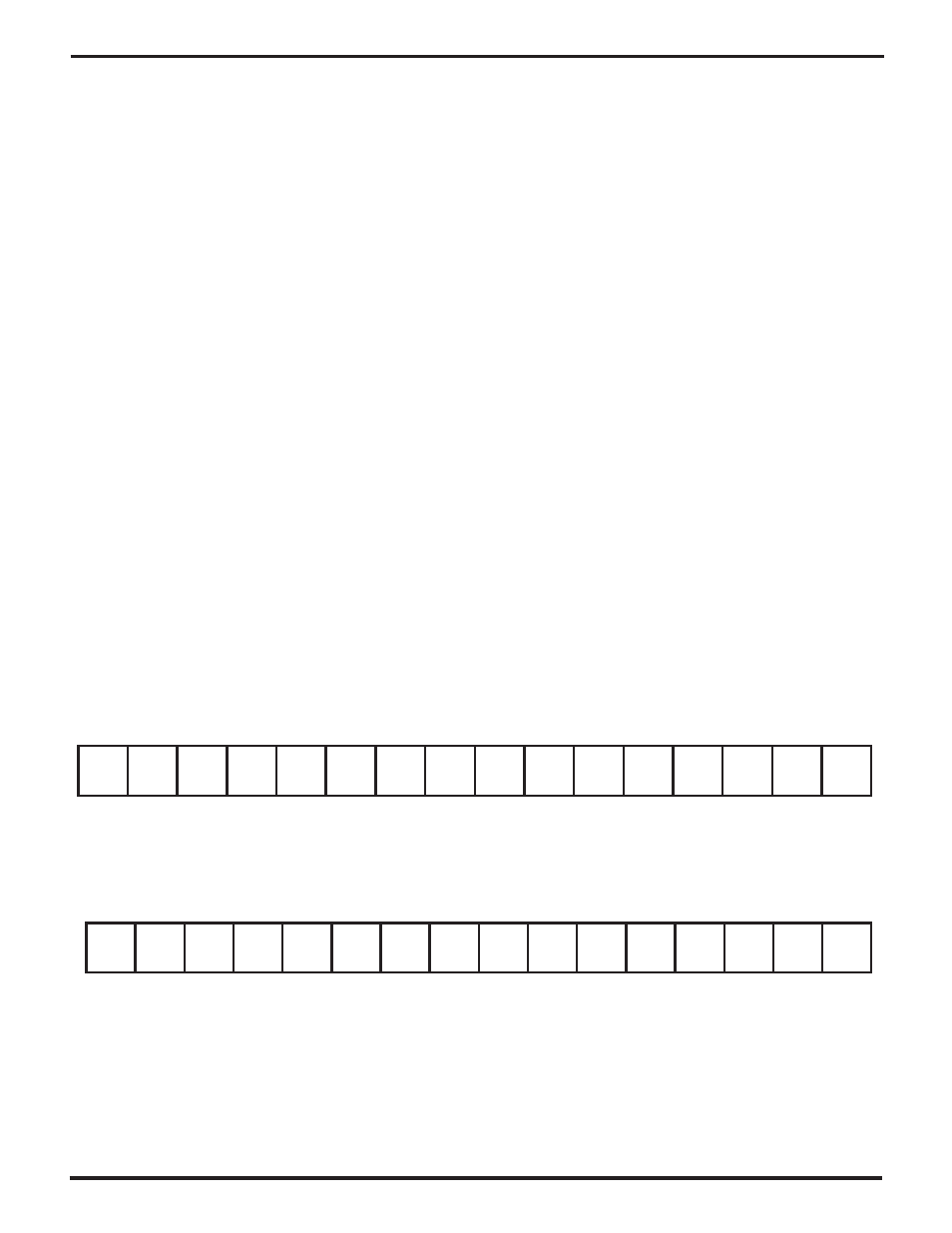

RxCUp

IA

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

RxCDn

IA

TxRDn

IA

TxCDn

IA

CTSUp

IA

DCDDn

IA

RCC

Under

IA

TxCUp

IA

RxRDn

IA

RxRUp

IA

TxRUp

IA

DCDUp

IA

CTSDn

IA

DPLL

DSync

IA

BRG1

IA

BRG0

IA

Figure 7-14. The Status Interrupt Control Register (SICR)

/RxC

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

RxCL/U

TxRL/U

TxCL/U

/CTS

DCDL/U

RCC

Under

L/U

/TxC

RxRL/U /RxREQ

/TxREQ

/DCD

CTSL/U

DPLL

DSync

L/U

BRG1

L/U

BRG0

L/U

Figure 7-15. The Miscellaneous Interrupt Status Register (MISR)

It is good programming practice to follow these two steps

with writing a “Select TICRHi=FIFO Status” command to

the TCSR, to protect the Request Level from inadvertent

modification when other parts of the software change the

IA bits in the TICR.

Code that writes or reads the Transmit Data Interrupt

Request threshold must ensure that no interrupt will occur

between the time it writes the “Select TICRHi=/INT Level”

command to the TCSR, and when it writes or reads the

value in the TICR, if such interrupts can lead to other code

writing a different Select command (for the FIFO Fill level

or DMA request threshold) to the TCSR.

Note that a Purge Tx FIFO (or Purge Rx and Tx FIFO)

command will typically make a channel immediately set its

Transmit Data IP bit. This will, in turn, make the channel

start requesting an interrupt on its /INT pin if:

■

it hadn’t been doing so,

■

the channel’s IEI pin is high,

■

its TD IE and MIE bits are 1, and

■

its TD IUS and all higher-priority IUS bits are 0.

As with all USC interrupts, a Transmit Data interrupt service

routine must explicitly clear the Transmit Data IP and IUS

bits by writing to the Daisy Chain Control Register (DCCR)

as described later; the bits aren’t cleared by simply writing

data into the TxFIFO.

UM009402-0201