Zilog Z16C30 User Manual

Page 130

7-2

Z16C30 USC

®

U

SER

'

S

M

ANUAL

UM97USC0100

Z

ILOG

7.2 INTERRUPT ACKNOWLEDGE DAISY-CHAINS

(Continued)

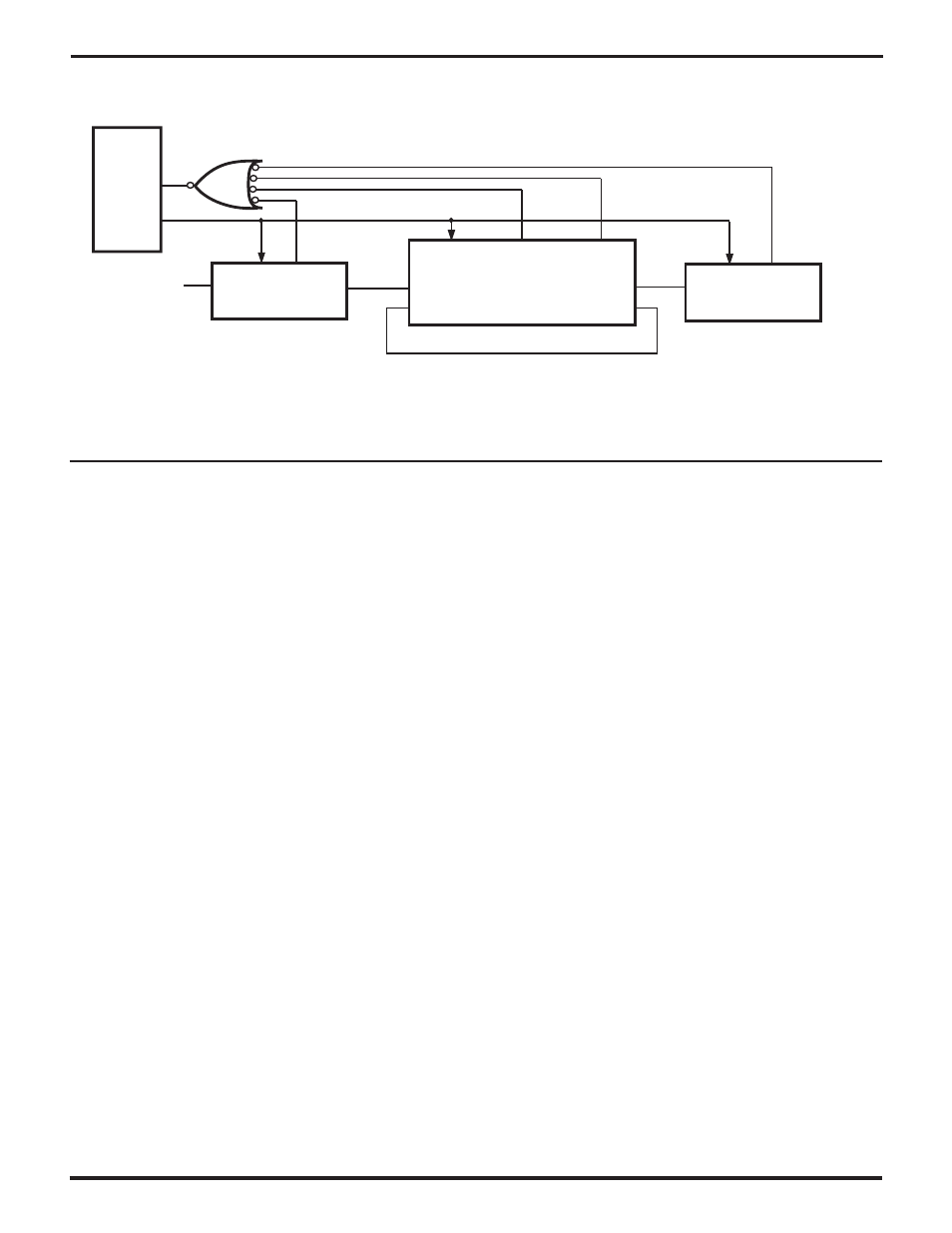

7.3 EXTERNAL INTERRUPT CONTROL LOGIC

There are two valid reasons why a system designer might

choose not to use an interrupt acknowledge daisy chain

(plus the less valid one of not being familiar with them).

First, in a system that includes many USC channels all

having similar baud rates and serial traffic, the strict priority

among channels that’s inherent in a daisy chain, might

endanger proper interrupt servicing for the channel(s) at

the low-priority end of the chain. In such cases, interrupt

service requirements may be more easily guaranteed by

using a central interrupt controller that distributes interrupt

acknowledgments among the channels on a round-robin

(rotating-priority) basis. Such schemes target “fairness”

rather than priority in interrupt servicing among the chan-

nels.

A second reason not to use a simple/wired interrupt daisy

chain would be in a system in which data rates vary over

a considerable range among several USC channels, and

are determined dynamically rather than being known as

the system is being designed. (A channel’s interrupt ser-

vicing requirements typically vary directly with its serial

data rate.) In such a system, external interrupt logic can

distribute interrupt acknowledge cycles using a dynamic

priority determined by each channel’s data rate.

Both rotating-priority and dynamic-priority systems can be

arranged as shown in Figure 7-2. The interrupt control

logic maintains the IEI inputs of the channels high most or

all of the time, so that the channels can assert their /INT

outputs. The logic may simply OR the /INT outputs of the

various channels to make the interrupt request to the

processor. Alternatively, in a dynamic-priority system with

a processor that supports multiple levels of interrupts, the

control logic may assign different channels to different

processor levels.

Regardless of how the interrupt control logic derives the

processor request, when the processor does an interrupt

acknowledge cycle, the logic must select a particular

device from among those requesting an interrupt, to “re-

ceive” the cycle. The control logic can implement this

choice in one of two ways. First, it can negate the IEI inputs

of all but one device, and then wait for the specified setup

time before presenting the cycle to all of the devices, using

the /PITACK or /SITACK signal and possible other bus

control signals. Or, it can simply present the cycle only to

the selected channel, typically using a single pulse on

/PITACK.

Host

MPU

/SITACK

or /PITACK

/INTA

/INTB

IEOB

IEOA

IEIA

IEIB

USC

IEI

IEO

Peripheral A

VCC

(NC)

IEI

IEO

Peripheral C

/IACK /IRQ

/IACK /IRQ

Figure 7-1. An Interrupt Daisy Chain

UM009402-0201