Zilog Z16C30 User Manual

Page 72

5-5

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

This relatively simple technique allows transmission of any

kind of data and assures uniqueness of the Flag sequence

within the data stream. (Uniqueness is assured as long as

line errors don’t occur.) This makes for simpler hardware

than with some character-oriented synchronous proto-

cols, in that the hardware only has to recognize a few bit

sequences. They include 0111111 for zero-bit-stuffing by

a Transmitter, 0111110 for bit removal by a Receiver, a

Flag sequence, and finally an Abort sequence. An Abort is

a zero followed by 7 or more ones.

As mentioned in the previous chapter, SDLC/HDLC proto-

cols match up well with NRZI-Space encoding to ensure

data transitions for clock resynchronization. This is be-

cause the Transmitter inverts NRZI-space data for every 0-

bit and there are never more than five 1-bits in succession

within a frame.

Finally, since the Flag-matching hardware operates with-

out regard for character boundaries, bit-oriented synchro-

nous protocols can handle frames that are any number of

bits in length. (In character-oriented synchronous proto-

cols, messages must be composed of an integer number

of characters.)

The USC can handle most variations of SDLC and HDLC

protocols, since it leaves the details of almost all such

variations to the host software. One variation with hardware

significance is Loop mode. In this mode, the Transmitter

can forward received data from the “preceding” station in

a loop of stations to the “next” one in the loop. When this

station has a frame to send, host software can load the start

of the frame into the TxFIFO and then enable the Transmit-

ter. The Transmitter then waits until it detects the transmit-

permission token called Go Ahead, which is the same as

the short-Abort sequence 01111111 in HDLC/ SDLC mode.

The Transmitter then changes this character to a Flag and

begins transmitting.

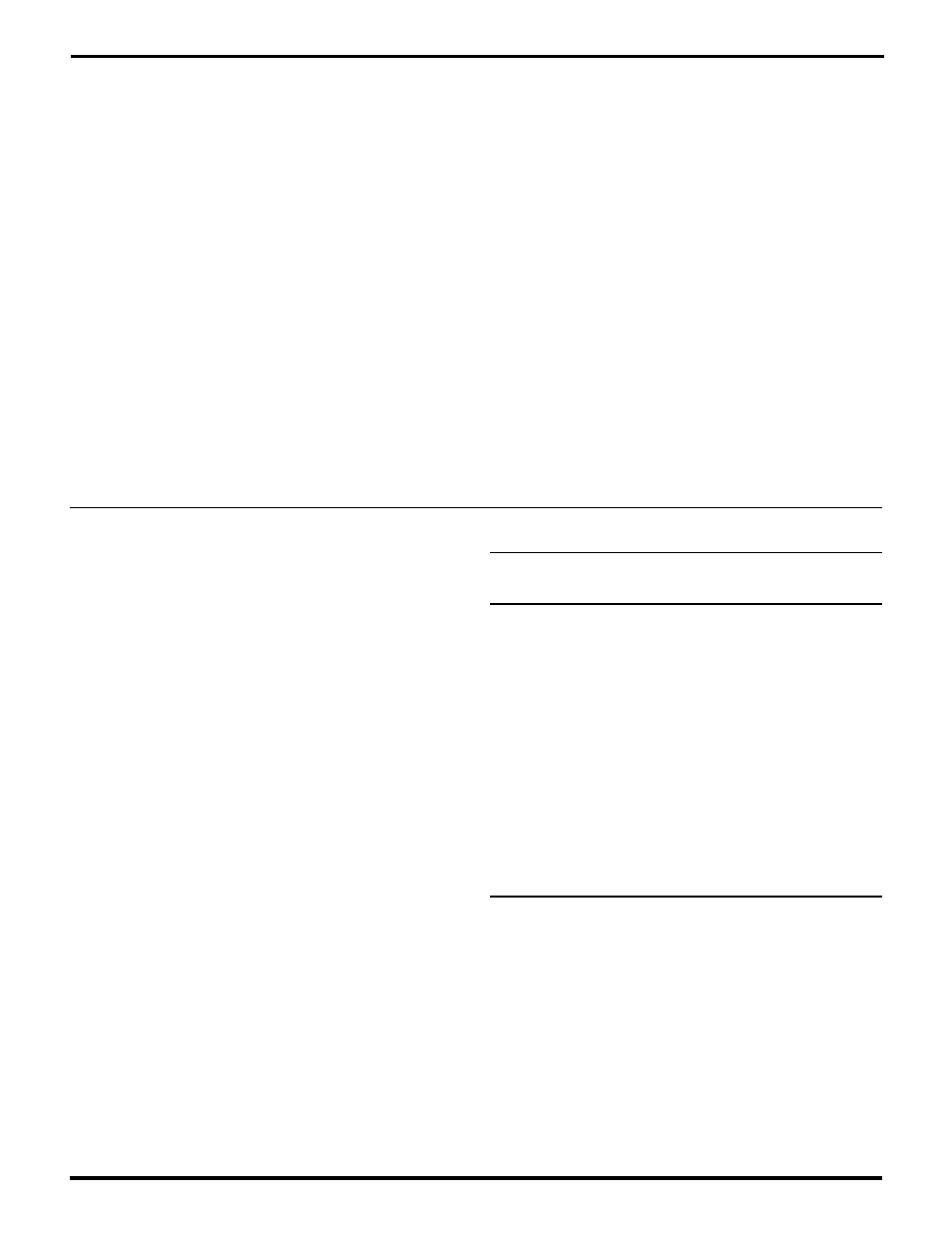

TxMode

RxMode

Value

(CMR11-8)

(CMR3-0)

0000

Asynchronous

Asynchronous

0001

—

External Sync

0010

Isochronous

Isochronous

0100

Monosync

Monosync

0101

Bisync

Bisync

0110

HDLC/SDLC

HDLC/SDLC

0111

Transp. Bisync

Transp. Bisync

1000

Nine-Bit

Nine-Bit

1001

802.3 (Ethernet)

802.3 (Ethernet)

1010

—

—

1011

—

—

1100

Slaved Monosync

—

1101

—

—

1110

HDLC/SDLC Loop

—

1111

—

—

Zilog reserves values shown above as “—” for future use;

they should not be programmed in the indicated field.

5.5 THE MODE REGISTERS (CMR, TMR AND RMR)

Three Mode registers in each channel of the USC control

the basic operation and serial protocol of the channel’s

Transmitter and Receiver.

The Channel Mode Register (CMR) selects among the

various communication protocols mentioned in the pre-

ceding sections. Figure 5-4 shows that the MSbyte con-

trols the mode of the Transmitter, while the LSbyte controls

that of the Receiver. Software can select the modes of the

two modules independently by writing bytes to the CMR,

or, on a 16-bit bus, it can set both modes simultaneously

using a 16-bit write.

Within each byte, the four LSbits select the major commu-

nications protocol. The coding for these fields is similar but

not identical because some modes apply only to the

Transmitter while others apply only to the Receiver:

UM009402-0201