Zilog Z16C30 User Manual

Page 105

5-38

Z16C30 USC

®

U

SER

'

S

M

ANUAL

UM97USC0100

Z

ILOG

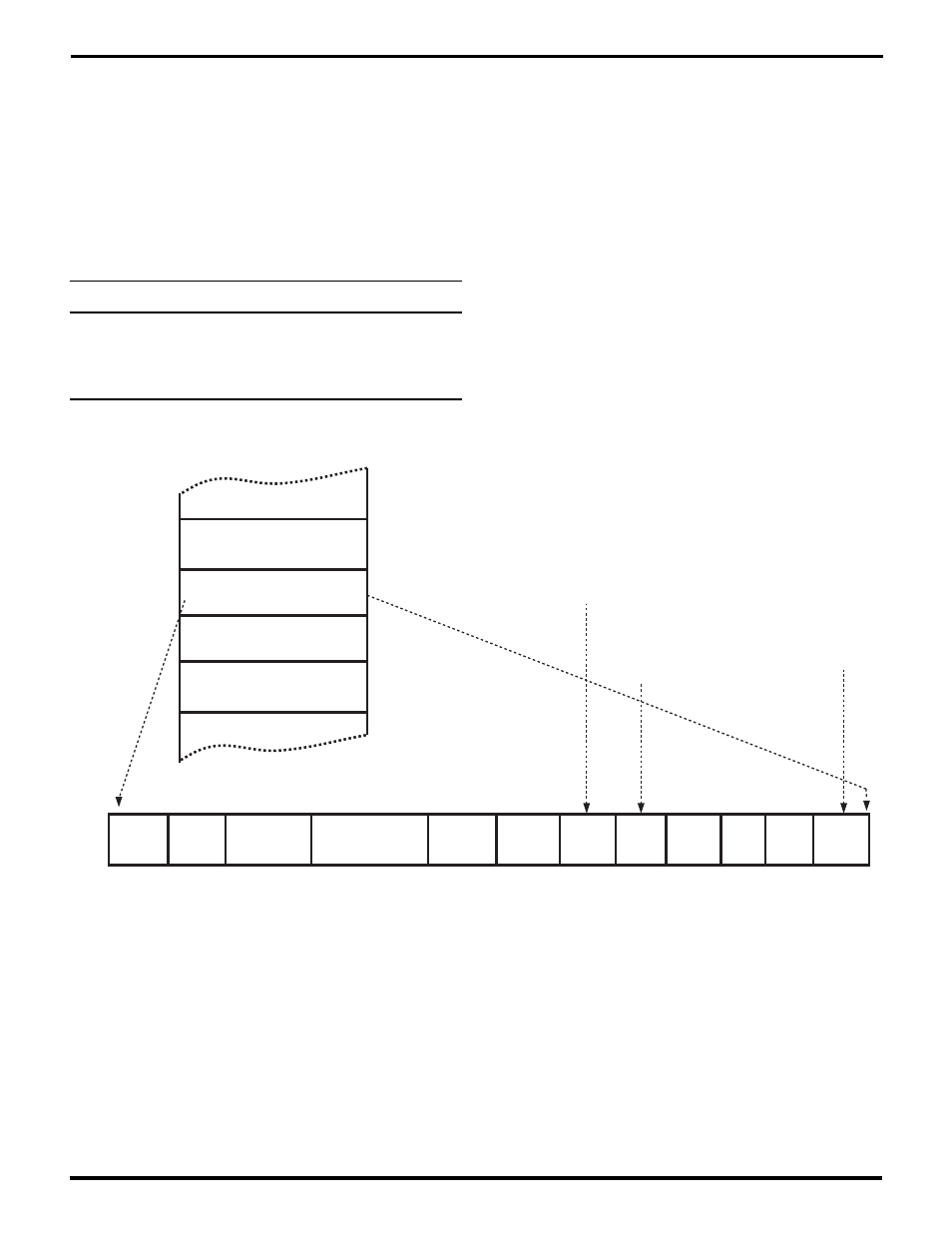

5.19.4 Receive Status Blocks

A USC Receiver sets the RxBound bit in the RxFIFO to

indicate the end of a frame, message, or word, in External

Sync, Transparent Bisync, 802.3, and HDLC/SDLC. In

these modes the Receiver can provide summary/status

information in the receive data stream, after the last char-

acter of the frame, message, or word. The

RxStatBlk

field

of the Channel Control Register (CCR7-6) controls whether

it does this. A channel interprets it as follows:

RxStatBlk

Kind of RSB’s used

00

No Receive Status Block

01

16-bit Receive Status Block

10

32-bit Receive Status Block

11

Reserved; do not program

If this field is either 01 or 10, the Receiver stores status from

the Receive Command/Status Register (RCSR) after the

frame. The 10 value makes the channel also store the

ending value of the Receive Character Counter in a sec-

ond 16-bit word after the RCSR status word. Figure 5-18

shows a 32-bit RSB.

Last 1 or 2 character(s)

of frame or message "N"

Status Word for

frame or message "N"

Ending RC Count for

frame or message "N"

First character(s) of

frame or message "N+1"

Address x

x+2

x+4

Address x+6

D15

D0

D15

D14

D11

D8

2ndBE 1stBE

00

RxResidue

D9

ShortF/

CVType

00

Rx

Bound

CRCE

/FE

PE

Rx

Over

RCC0

D4

D3

D2

D1

D0

Always

1

Different

from

RCSR

RCCF

Ovflo

Only on

USCs manufactured

since June 1993

D5

Figure 5-18. A 32-bit Receive Status Block in a DMA Buffer

UM009402-0201