2 asynchronous modes (continued) – Zilog Z16C30 User Manual

Page 69

5-2

Z16C30 USC

®

U

SER

'

S

M

ANUAL

UM97USC0100

Z

ILOG

5.2 ASYNCHRONOUS MODES

(Continued)

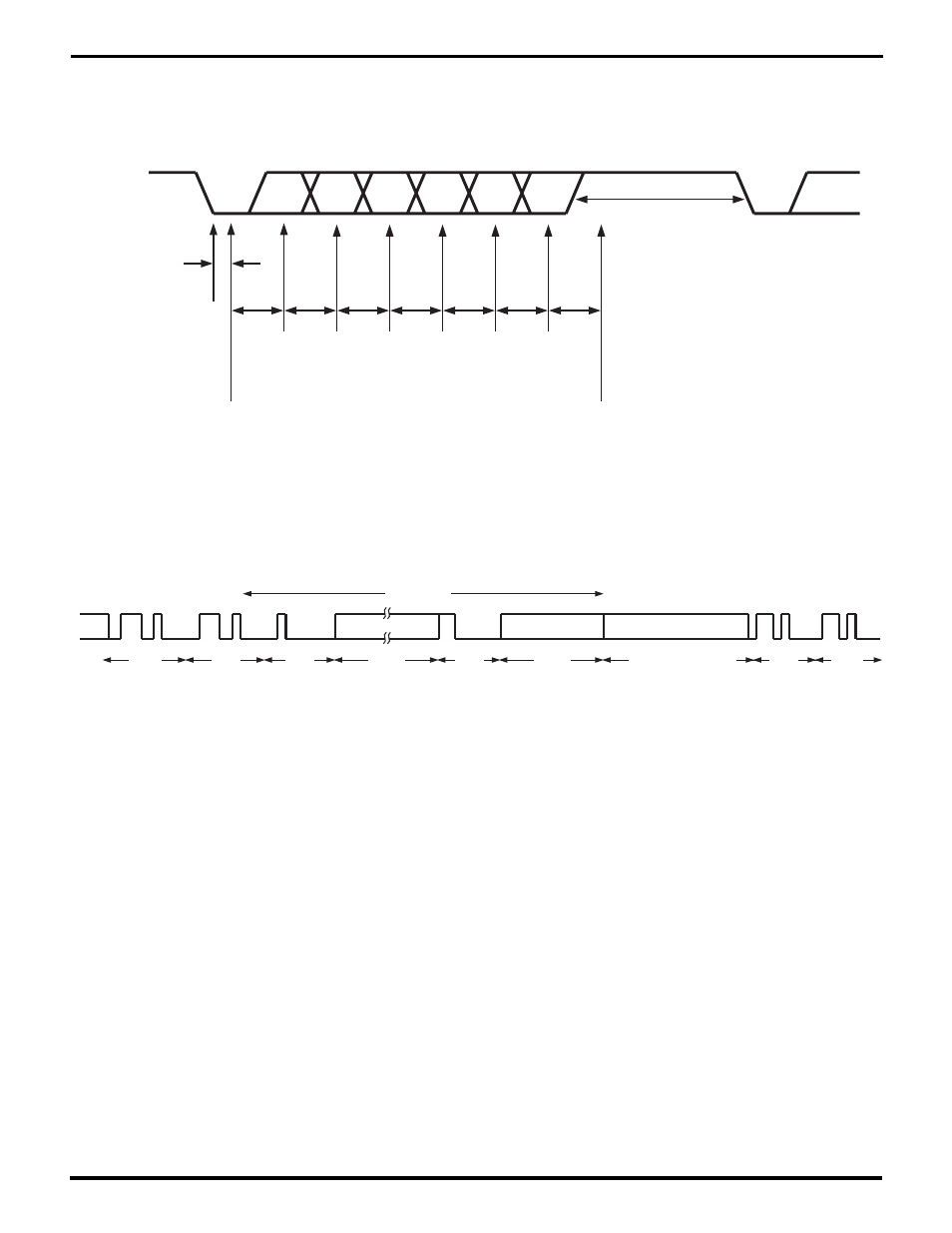

Minimum 1 Bit Time

(except for "Shaving")

5 to 8 Data Bits,

Plus Optional Parity Bit

Start

Bit

Start

Bit

Stop

Bit

1/2 Bit Time

Receiver detects

Falling Edge

Receiver validates

Start Bit

All 1 Bit TIme

Receiver Samples Data

(and Parity?) Bits

Receiver checks

Stop Bit

Figure 5-1. Asynchronous Data

May be SYNs, Mark,

Space, or Not Driven

SYN

(16)

SYN

(16)

CRC

ETX

(03)

Data

STX

(02)

STX

(16)

SYN

(16)

Message

Figure 5-2. Character Oriented Synchronous Data

UM009402-0201

See also other documents in the category Zilog Sensors:

- S3F94C8 (11 pages)

- S3F80QB (29 pages)

- S3F8S19 (38 pages)

- Z51F6412 (96 pages)

- Z51F6412 (54 pages)

- Z51F6412 (55 pages)

- EZ80F93 (11 pages)

- Z16F6411 (20 pages)

- Z16F6411 (216 pages)

- EZ80F93 (13 pages)

- ZMOT0BSB (314 pages)

- ZMOT0BSB (582 pages)

- Z8F083A (14 pages)

- Z8F2480 (17 pages)

- Z8F082A (18 pages)

- Z8F082A (15 pages)

- Z8F6423 (83 pages)

- Z8F0822 (17 pages)

- Z8F2480 (19 pages)

- Z8F2480 (18 pages)

- Z8F6423 (18 pages)

- Z8F6423 (27 pages)

- Z8F6482 (50 pages)

- EZ80F915 (411 pages)

- EZ80F91NAA (34 pages)

- EZ80F91 (41 pages)

- EZ80L92 (40 pages)

- EZ80L92 (26 pages)

- EZ80L92 (79 pages)

- EZ80F91GA (469 pages)

- EZ80L92 (10 pages)

- eZ80F92 (87 pages)

- Z16FMC6 (520 pages)

- Z8FMC16 (26 pages)

- Z16FMC6 (41 pages)

- ZUSBOPTS (38 pages)

- ZUSBOPTS (59 pages)

- Z16FMC6 (26 pages)

- Z16FMC6 (8 pages)

- ZMOT1AHH (25 pages)

- ZMOT0BSB (34 pages)

- EZ80F915 (78 pages)

- EZ80190 (87 pages)

- EZ80L92 (86 pages)

- EZ80F91GA (127 pages)