Zilog Z16C30 User Manual

Page 168

8-13

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Clear

RCCF

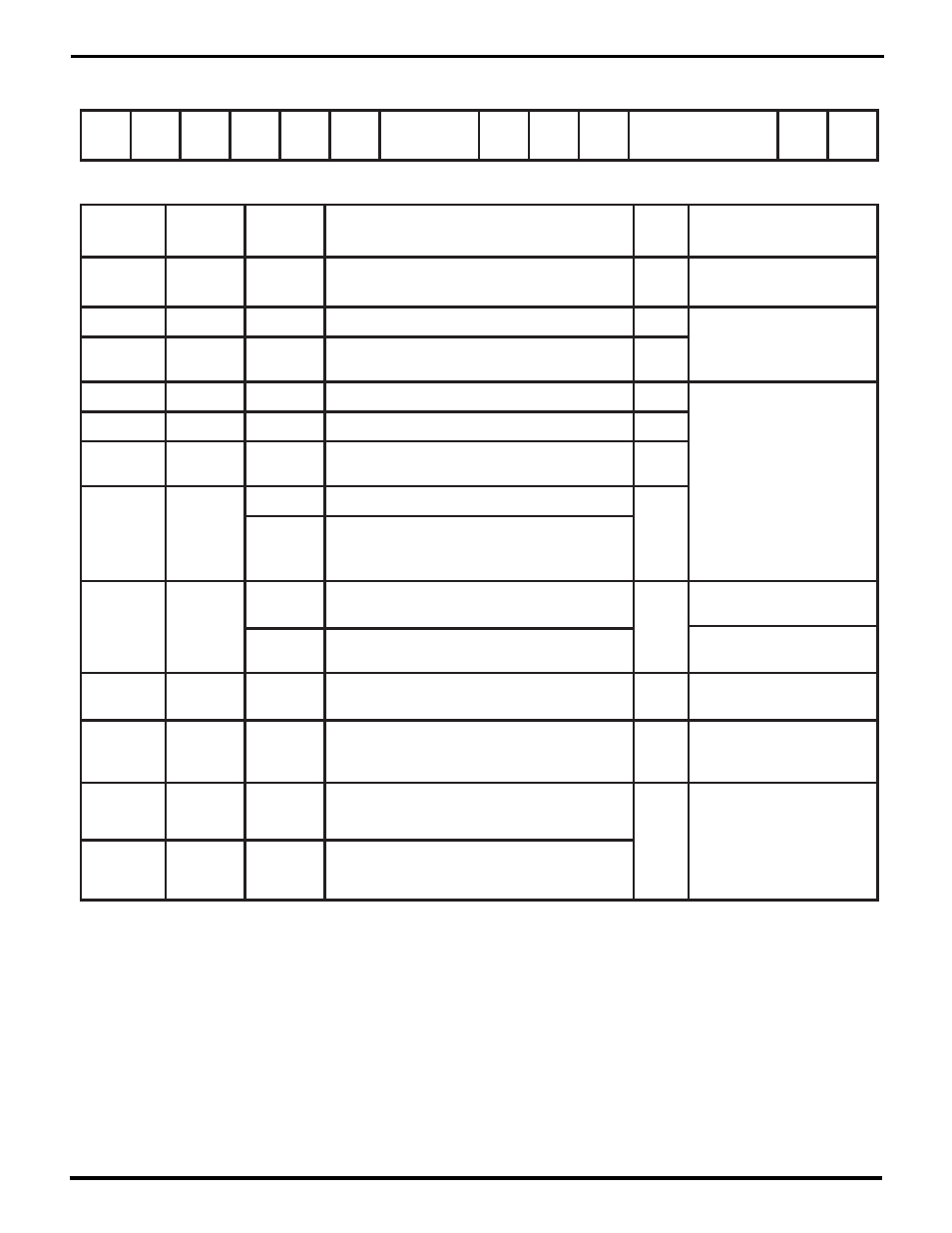

Channel Command/Status Register (CCSR)

Register Address 0 b 00010

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

TxResidue

CCSR15

DPLL

1Miss

DPLLEdge

On

Loop

Loop

Send

RCCF Ovflo

1=RCC FIFO overflow (4+1 frames)

RO

5: DMA Support Features:

The RCC FIFO

CCSR7

OnLoop

1=Transmit is or has been active (cleared only

by leaving Slave Monosync mode)

RO

5: Slaved Monosync Mode

5: HDLC/SDLC Loop Mode

Slaved

Monosync

Resrvd

RCCF

Ovflo

RCCF

Avail

DPLL

Sync

DPLL

2Miss

RCC

Enabled

CCSR14

RCCF Avail

1=RCC FIFO not empty

RO

CCSR13

Clear RCCF

1=purge RCC FIFO, clear RCCF Ovflo and

RCCF Avail to 0

WO

CCSR12

DPLL Sync

1=DPLL in sync

R,W1C

4: More About the DPLL

CCSR11

DPLL2Miss

1=DPLL has seen two consecutive missing clocks

R,W1C

Biphase

CCSR10

DPLL1Miss

1=DPLL has seen a missing clock

R,W1C

Biphase,

CVOK=0

CCSR9-8

DPLLEdge

00=DPLL resyncs on rising and falling edges

RW

NRZ

modes

only

01=DPLL sees rising edges only;

10=DPLL sees falling edges only;

11=DPLL free-runs like CTR1,0

1=USC has inserted itself in the loop

H/SDLC

Loop

CCSR6

LoopSend

1=Transmit actively sending;

0=Transmit repeating Receive

RO

5: HDLC/SDLC Loop Mode

H/SDLC

Loop

CCSR4-2

TxResidue

000=last character of Transmit frame contains

8 bits; 001-111=last character contains 1-7 bits

RW

5: HDLC/SDLC Mode:

Frame Length Residuals

CCSR1

/TxACK

1=/TxACK pin is low

RO

4: The /TxACK and /RxACK

Pins

TxAMode

(HCR7-6)

=00

/TxACK /RxACK

H/SDLC,

H/SDLC

Loop

CCSR0

/RxACK

RxAMode

(HCR3-2)

=00

1=/RxACK pin is low

RW = Read/Write, RO = Read Only, WO = Write Only – for other codes see p. 8-10.

UM009402-0201