Zilog Z16C30 User Manual

Page 188

8-33

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

TCmd

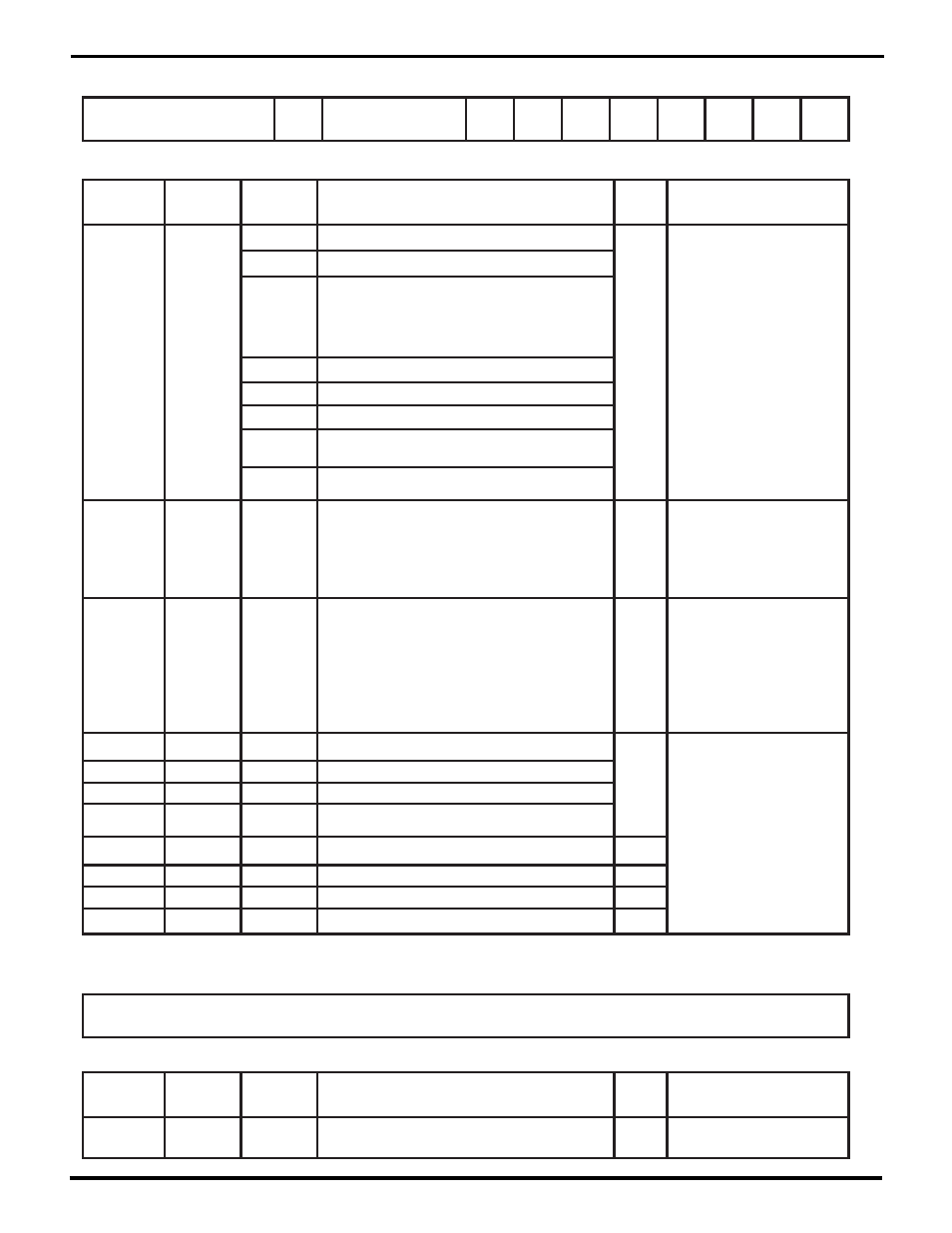

Transmit Command/Status Register (TCSR)

Register Address 0 b 11010

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

Pre

Sent

TCSR15-12

Under

Wait

TxIdle

Idle

Sent

Abort

Sent

EOF/

EOM

Sent

CRC

Sent

All

Sent

Tx

Under

Tx

Empty

TCmd

Sync

0000=no operation; 0001=reserved

0010=Clear Tx CRC Generator

0011, 0100=reserved;

0101=Select TICRHi=TxFIFO Status;

0110=Select TICRHi=/INT Level;

0111=Select TICRHi=/TxREQ Level

WO

5: Commands

TICR2=1

1000=Send Frame/Message

H/SDLC

1001=Send Abort

101x=reserved

T.Bisync

1100=Enable DLE Insertion;

1101=Disable DLE Insertion

Sync

1110=Clear EOF/EOM;

1111=Set EOF/EOM

TCSR10-8

TxIdle

Selects the Transmit idle line condition:

000=the default for TxMode (sync/Flag/Mark)

001=alternating zeroes and ones

010=continuous zeroes

011=continuous ones

100=reserved

101=alternating Mark and Space

110=continuous Space (TxD low)

111=continuous Mark (TxD high)

RW

5: Between Messages,

Frames, or Characters

TCSR7

PreSent

1=Transmitter has finished sending Preamble

R,W1U

5: Status Reporting:

Detailed Status in the TCSR

Sync

TCSR6

IdleSent

1=Transmitter has sent Idle condition

TCSR5

AbortSent

1=Transmitter has sent Abort

H/SDLC

TCSR4

EOF/EOM

Sent

1=Transmitter has sent End of Frame/End

of Message

Sync

TCSR3

CRCSent

1=Transmitter has sent a CRC code

Sync

TCSR2

AllSent

1=last bit has gone out onto TxD

Async

RO

TCSR1

TxUnder

1=Transmitter has Underflowed

R,W1U

TCSR0

TxEmpty

1=TxFIFO is empty

RO

TCSR11

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Starting value for Transmit Character Counter

Transmit Count Limit Register (TCLR)

Register Address 0 b 11101

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

TCLR15-0

Starting value for TCC: 0=disable TCC;

else length of next frame/message

RW

5: DMA Support Features:

The Character Counters

UnderWait

Sync

1=interlock Transmitter from

Tx underrun until Send Frame

command. Also, if TxCtrlBlk

(CCR15-14) is 10 = 32-bit TCBs,

delay start of frame transmission

until TxFIFO is full or complete frame

written to TxFIFO

5: Handling Overruns and

Underruns: Tx Underruns

RW = Read/Write, RO = Read Only, WO = Write Only – for other codes see p. 8-10.

UM009402-0201