5 more about the dpll (continued), 6 the rxd and txd pins – Zilog Z16C30 User Manual

Page 59

4-10

Z16C30 USC

®

U

SER

'

S

M

ANUAL

UM97USC0100

Z

ILOG

4.5 MORE ABOUT THE DPLL

(Continued)

After software sets up the DPLL, three bits in the Channel

Command/Status Register (CCSR) provide the operating

interface. The logic enters a “fast sync mode” when soft-

ware writes a 1 to the

DPLLSync

bit (CCSR12), or in a

Biphase mode when it detects two consecutive missing

clocks. In this mode, the next RxD transition (that’s allowed

by the DPLLEdge field) resynchronizes the DPLL counter

and puts the DPLL “back in sync”.

The DPLL watches the RxD line for transitions, and classi-

fies them as either clock or data. Depending on the

position of transitions within each bit cell, the logic adjusts

the phase of the DPLL output clock to synchronize the

clock with the bit cell boundaries of the incoming data.

“Fast Sync” tells the DPLL that the NEXT edge it sees is the

one to synchronize to; otherwise the DPLL has to see “n”

correct edges before becoming “in sync.” “n” is about

three for X8 mode, six for X16, and 12 for X32.

The time required to get in sync in the worst case is thus a

function of the data encoding method, as well as the data

on the line. The key issue is the number of “edges” the

DPLL sees on RxD.

The DPLLSync bit in the Channel Command/Status Regis-

ter (CCSR12) reads as 1 if the DPLL is in sync. The

DPLL2Miss

bit (CCSR11) reads as 1 if the DPLL is in a

biphase mode and has detected missing clocks in two

consecutive bit cells. The

DPLL1Miss

bit (CCSR10) reads

as 1 if the DPLL is in a biphase mode, the CVOK bit

(HCR12) is 0, and the DPLL has detected a missing clock

in at least one cell. Once DPLL2Miss or DPLL1Miss is 1, it

continues to read that way until software writes a 1 to it.

Writing a 0 to any of DPLLSync, DPLL2Miss, or DPLL1Miss

has no effect on the DPLL logic.

The channel sets the

DPLLDSync L/U

bit when it loses

sync in a Biphase mode. This bit is similar to DPLL2Miss in

that once it’s set, it stays that way until software writes a 1

to the bit to “unlatch” it. Chapter 7 explains how to program

a channel so that it interrupts the host processor when it

sets DPLLDSync.

4.6 THE RXD AND TXD PINS

In some sense these are the most important pins on a USC.

Typically they carry the serial input to the Receiver and the

serial output of the Transmitter respectively. Figure 4-6

shows the I/O Control Register. Its

TxDMode

field (IOCR7-

6) allows software to control the function of TxD:

TxDMode

Function of the TxD pin

00

Totem-pole Transmitter output

01

High-impedance state

10

Low output

11

High output

Software can use the ability to drive TxD low to generate a

Break condition in Asynchronous applications. The dura-

tion of such a Break is fully under software control.

The ability to put the TxD pin in a high-impedance state

allows software to use the USC in “serial bus” schemes that

include multiple senders on the same signal line. (But note

that the TxDMode field resets to 00, so that the channel

drives TxD after a Reset until the software programs

TxDMode to 01.) The ability for direct programmable

control over the TxD pin allows software to “bit-bang”

unusual/occasional serial protocol requirements, while

keeping the USC’s full power for more standard and

everyday communications.

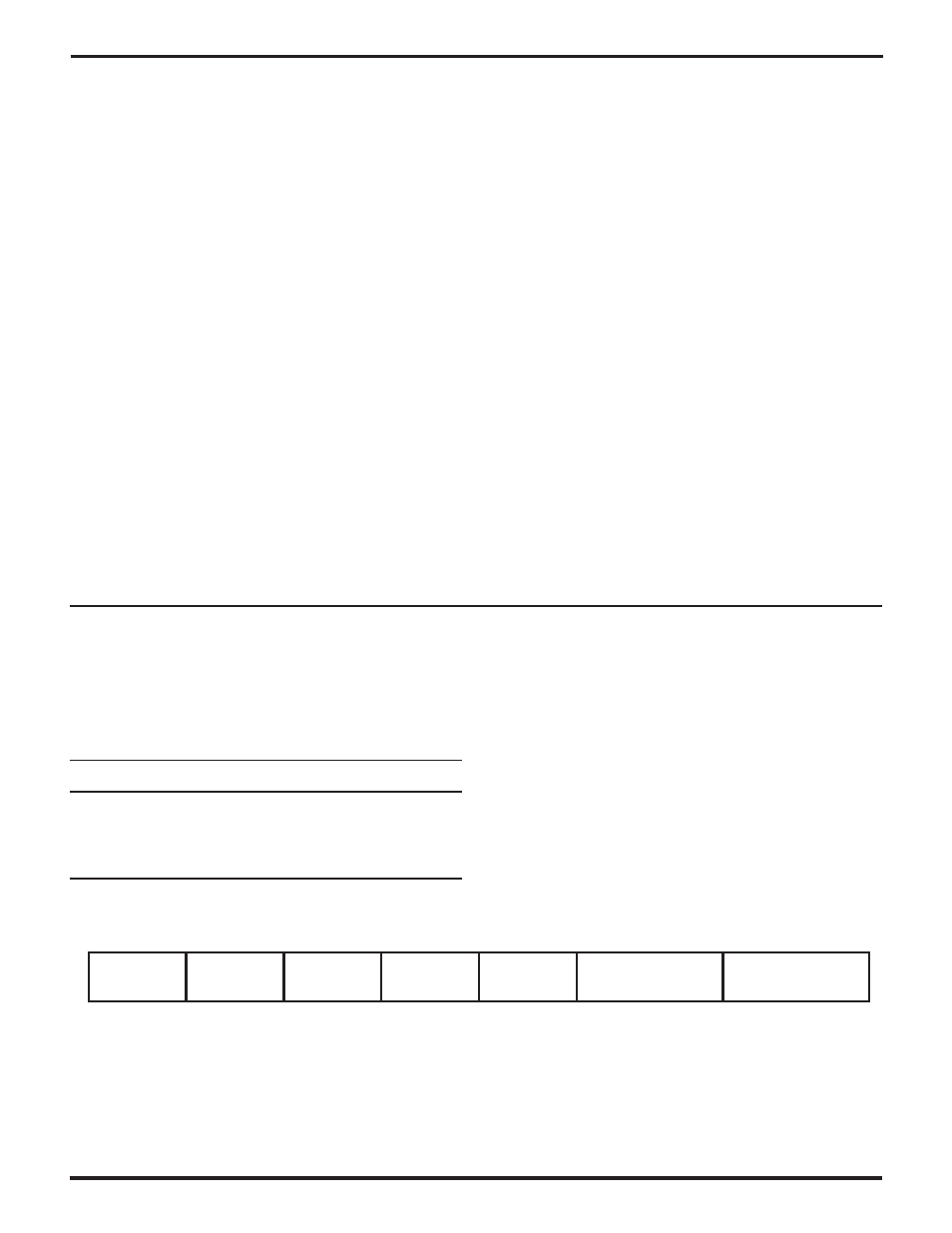

DCDMode

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

CTSMode

RxRMode

TxRMode

TxCMode

TxDMode

RxCMode

Figure 4-6. The Input/Output Control Register (IOCR)

UM009402-0201