Zilog Z16C30 User Manual

Page 169

8-14

Z16C30 USC

®

U

SER

'

S

M

ANUAL

Z

ILOG

UM97USC0100

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

15

Wait4

Tx Trig

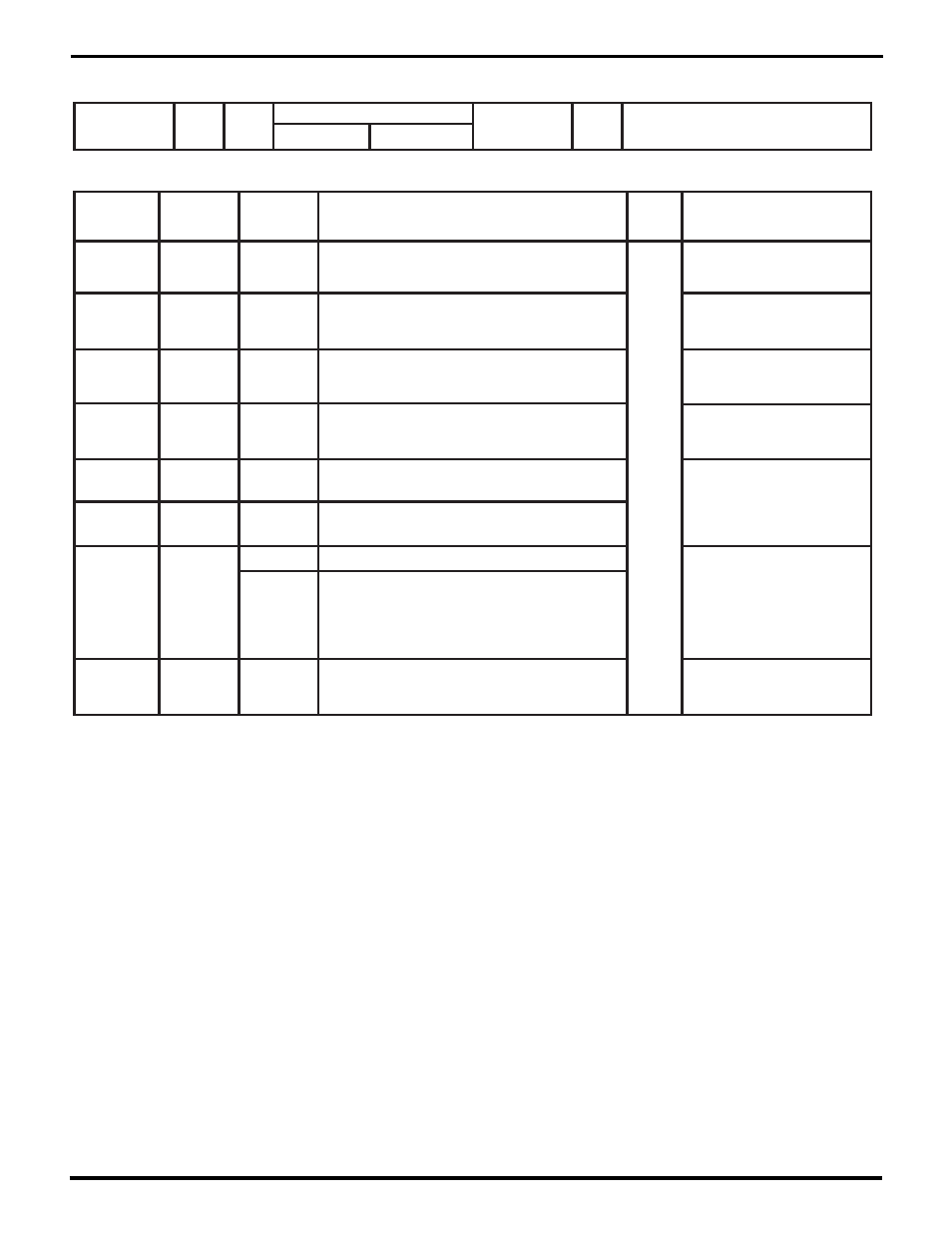

Channel Control Register (CCR)

Register Address 0 b 00011

Bit(s)

Field/Bit

Name

Conditions

/Context

Description

RW

Status

Ref Chapter: Section

Reserved (0)

CCR15-14

Async:TxShaveL

RxStatBlk

TxCtrlBlk

00=don't use Transmit Control Blocks;

10=use 32-bit TCB's

RW

5: DMA Support Features:

Transmit Control Blocks

Wait4

Rx Trig

TxCtrlBlk

Flag

Pre

Amble

CCR13

Wait4TxTrig

Sync:TxPreL

Sync:TxPrePat

Sync

1=hold Transmit DMA Request between

frames/messages, until software issues

"Trigger Tx DMA" command

5: Synchronizing Frames/

Messages with Software

Response

CCR11-8

TxShaveL

Async,

CMR15=1

shave the number of Stop bits

specified by TxSubMode CMR14

by (15 minus the value in this field)/16 bit times

5: Asynchronous Mode

CCR11-10

TxPreL

Sync w/

Preamble

00=send 8-bit Preamble; 01=16-bit;

10=32-bit; 11=64-bit

5: Between Frames,

Messages, or Characters

CCR9-8

TxPrePat

Sync w/

Preamble

00=all-zero Preamble; 01=all ones;

10=101010...; 11=010101...

5: DMA Support Features:

Receive Status Blocks

CCR7-6

RxStatBlk

00=do not use Receive Status Blocks;

Ext Sync,

T. Bisync,

H/SDLC,

802.3,

01=use 16-bit RSB's;

10=use 32-bit RSB's

5: Synchronizing Frames/

Messages with Software

Response

CCR5

Wait4

RxTrig

1=hold Receive DMA Request between frames/

messages, until software issues "Trigger Rx

DMA" command

Sync

CCR12

Flag

Preamble

H/SDLC,

CCR9-8

=01

1=send Flags as Preamble

5: Between Frames,

Messages, or Characters

RW = Read/Write, RO = Read Only, WO = Write Only – for other codes see p. 8-10.

UM009402-0201